IBM0316409C IBM0316809C

IBM03164B9C 16Mb Synchronous DRAM-Die Revision D

IBM0316169C

## Features

• High Performance:

|                 |                   | -80<br>CL=3 | -360<br>CL=3 | -10<br>CL=3 | Units |

|-----------------|-------------------|-------------|--------------|-------------|-------|

| f <sub>СК</sub> | Clock Frequency   | 125         | 100          | 100         | MHz   |

| t <sub>CK</sub> | Clock Cycle       | 8           | 10           | 10          | ns    |

| t <sub>AC</sub> | Clock Access Time | 6           | 5.5          | 8           | ns    |

- Single Pulsed RAS Interface

- Fully Synchronous to Positive Clock Edge

- Dual Banks controlled by A11 (Bank Select)

- Programmable CAS Latency: 1,2,3

- Programmable Burst Length: 1,2,4,8,full-page

- Programmable Wrap Sequence: Sequential or Interleave

- Multiple Burst Read with Single Write Option

- Automatic and Controlled Precharge Command

- Data Mask for Read/Write control (x4, x8)

- Dual Data Mask for byte control (x16)

- Auto Refresh (CBR), Self Refresh (SR)

- Suspend Mode and Power Down Mode

- 4096 refresh cycles/64ms

- Random Column Address every CLK (1-N Rule)

- Single  $3.3V \pm 0.3V$  Power Supply

- Supports LVTTL I/O interface

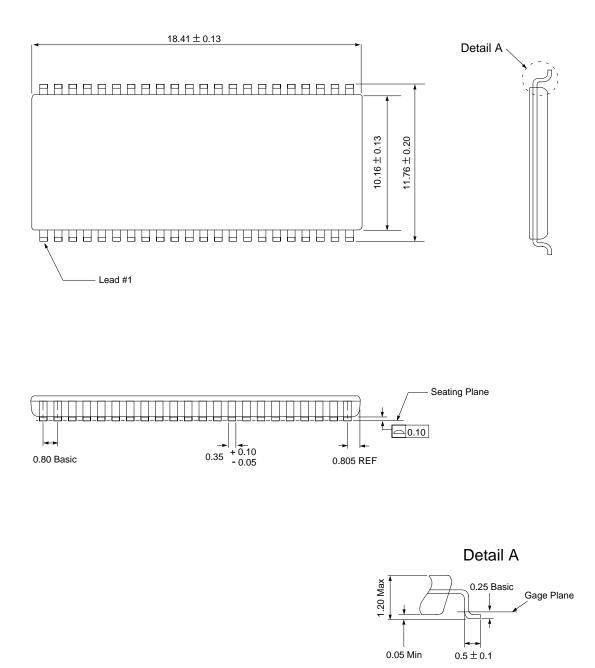

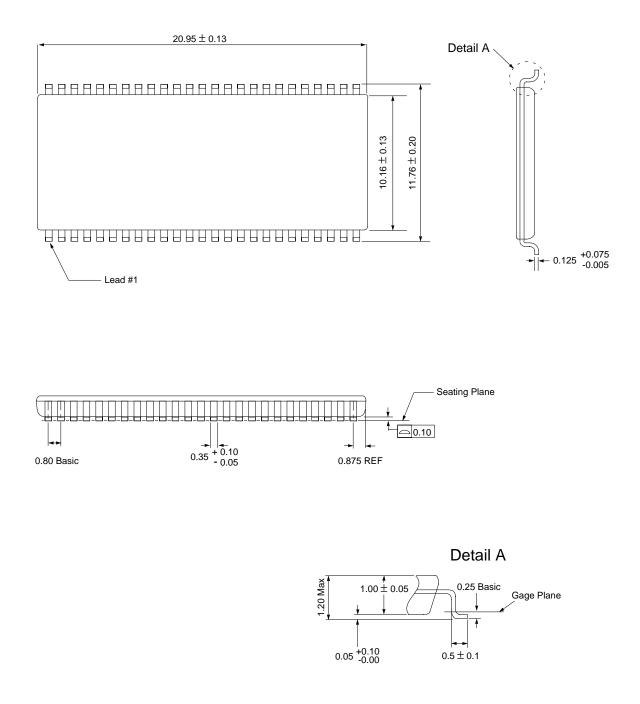

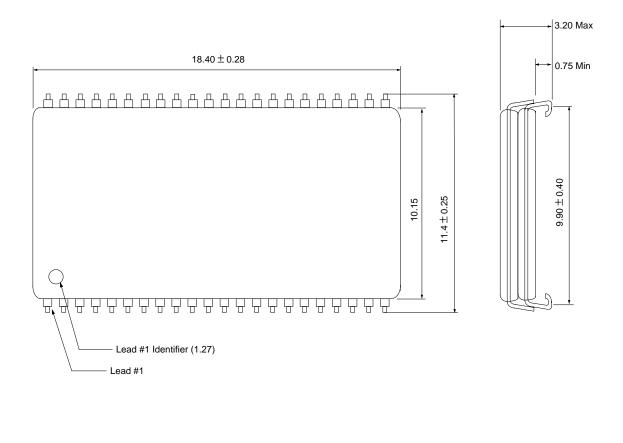

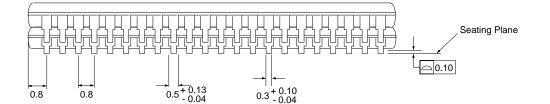

- Package: 44 pin 400 mil TSOP-Type II (x4,x8) 50 pin 400 mil TSOP-Type II (x16) 2-High Stack TSOJ

#### Description

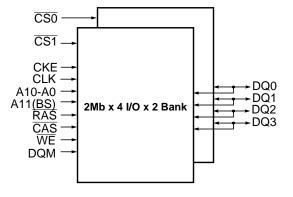

IBM's 0316409C, 0316809C, and 0316169C are dual bank Synchronous DRAMs organized as 2Mbit x 4 I/O x 2 Bank, 1Mbit x 8 I/O x 2 Bank, and 512Kbit x 16 I/O x 2 Bank, respectively. These devices support LVTTL I/O interface levels. A stacked version of the x 4 component is also offered. These synchronous devices achieve high speed data transfer rates of up to 125 MHz. The chip is fabricated with IBM's advanced 16Mbit CMOS DRAM process technology.

The device is designed to comply with all JEDEC standards set for synchronous DRAM products, both electrically and mechanically. All of the control, address and data input/output circuits are synchronized with the positive edge of an externally supplied clock (CLK).

Internal chip operating modes are defined by combinations of  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ , and  $\overline{CS}$  and a command decoder initiates the necessary timings for each operation. A twelve bit address bus accepts address data in the conventional  $\overline{RAS}/\overline{CAS}$  multiplexing style. Eleven row addresses (A0-A10) and a bank select address (A11) are strobed with  $\overline{RAS}$ . Ten column addresses (A0-A9) plus A10 and a bank select address (A11) are strobed with  $\overline{CAS}$ . Column

address A9 is dropped on the x8 device and column addresses A8 and A9 are dropped on the x16 device. Access to the lower or upper DRAM in a stacked device is controlled by  $\overline{CS0}$  and  $\overline{CS1}$ .

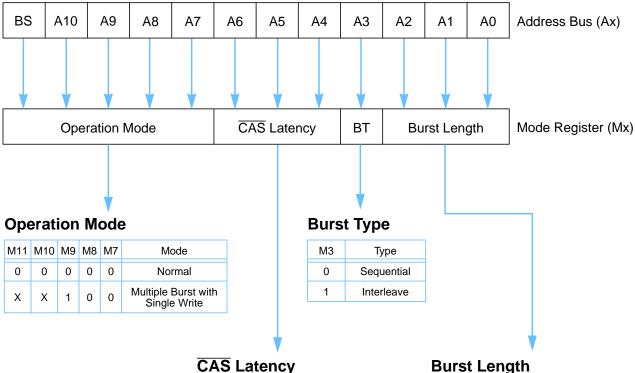

Prior to any access operation, the  $\overline{CAS}$  latency, burst length, and burst sequence must be programmed into the device by address inputs A0-A11 during a mode register set cycle. In addition, it is possible to program a multiple burst sequence with single write cycle for write through cache operation.

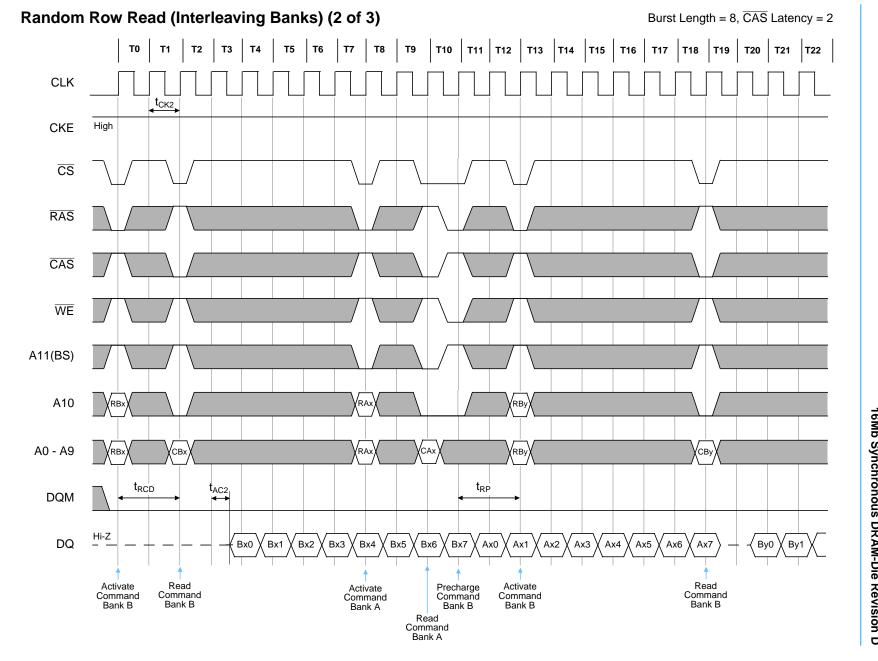

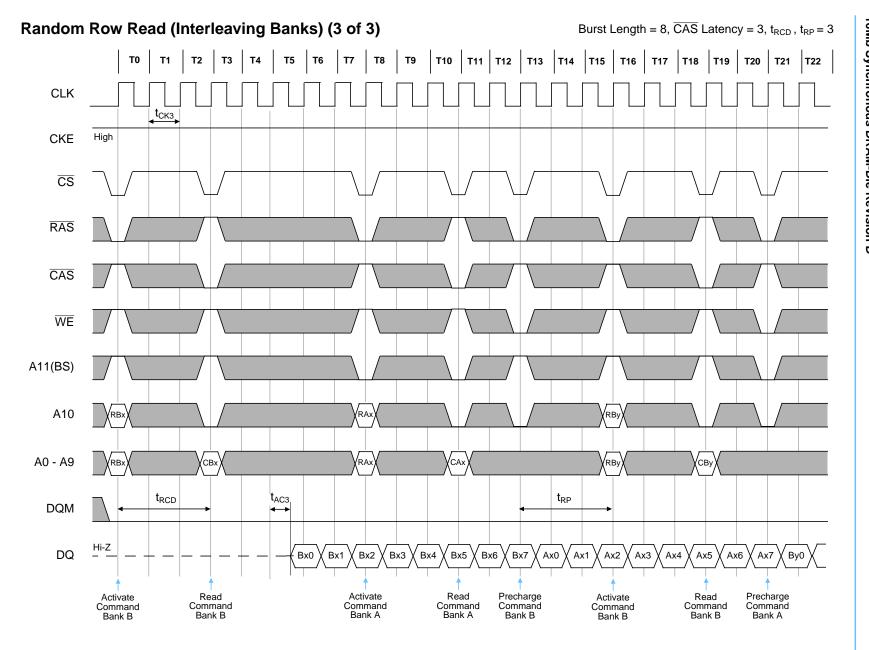

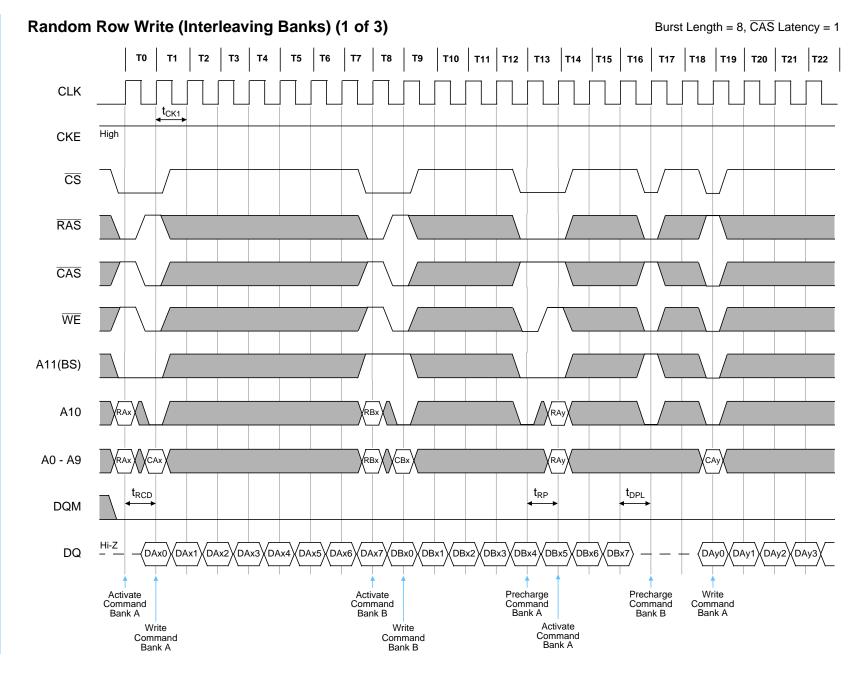

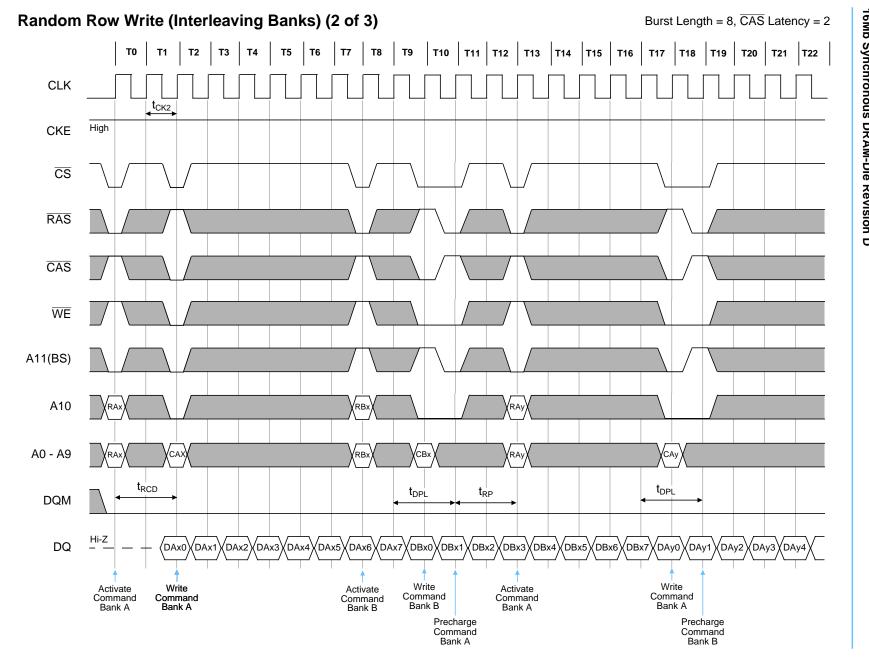

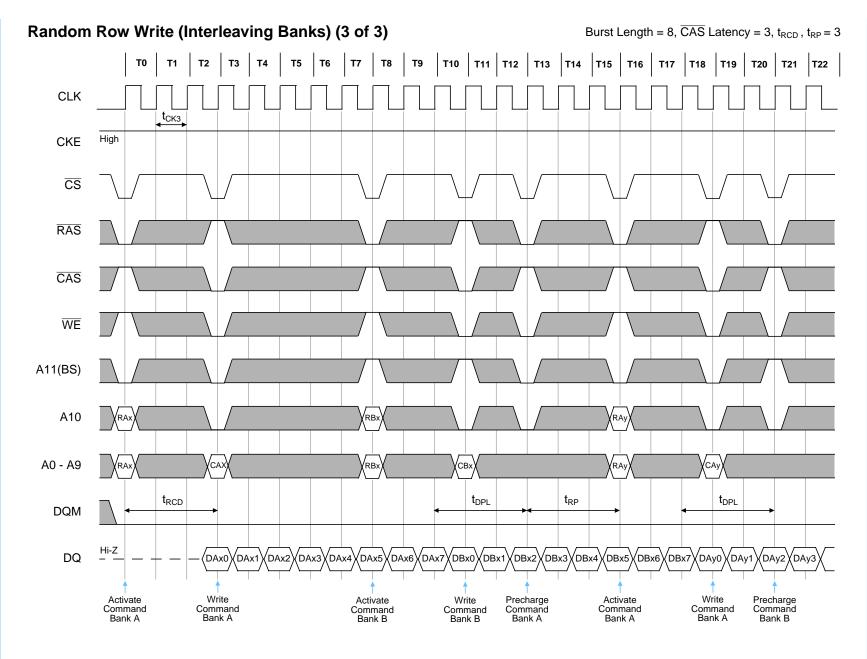

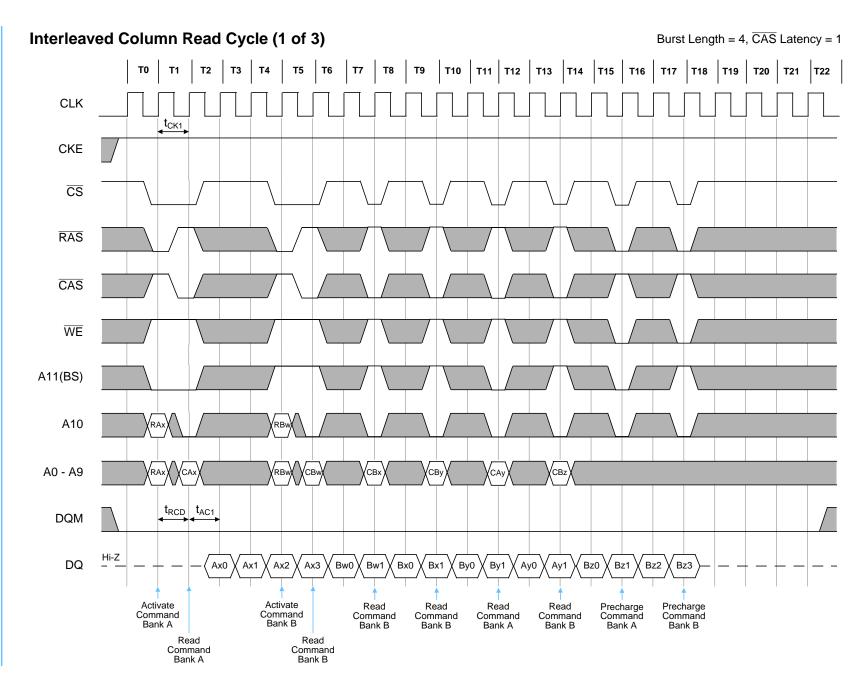

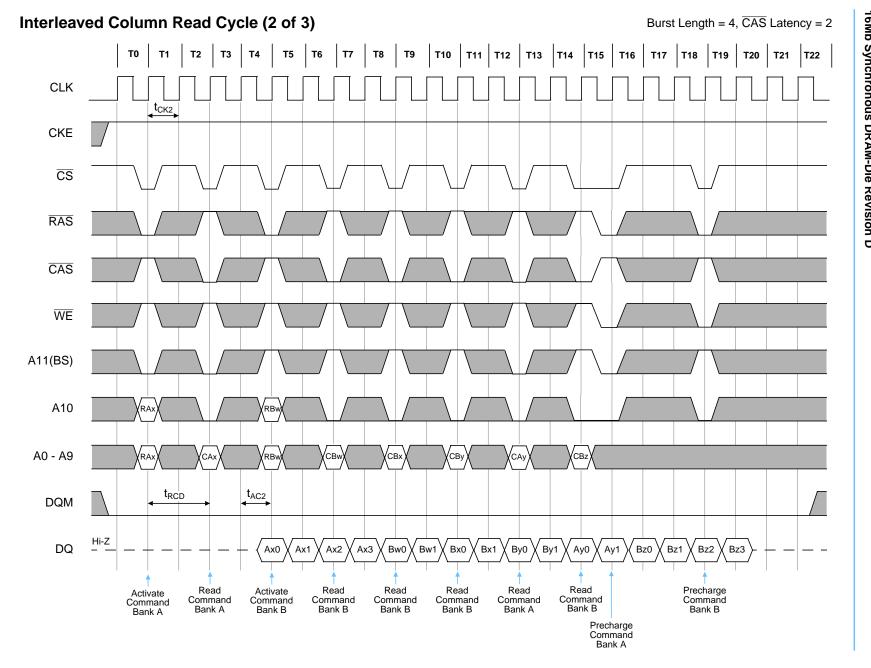

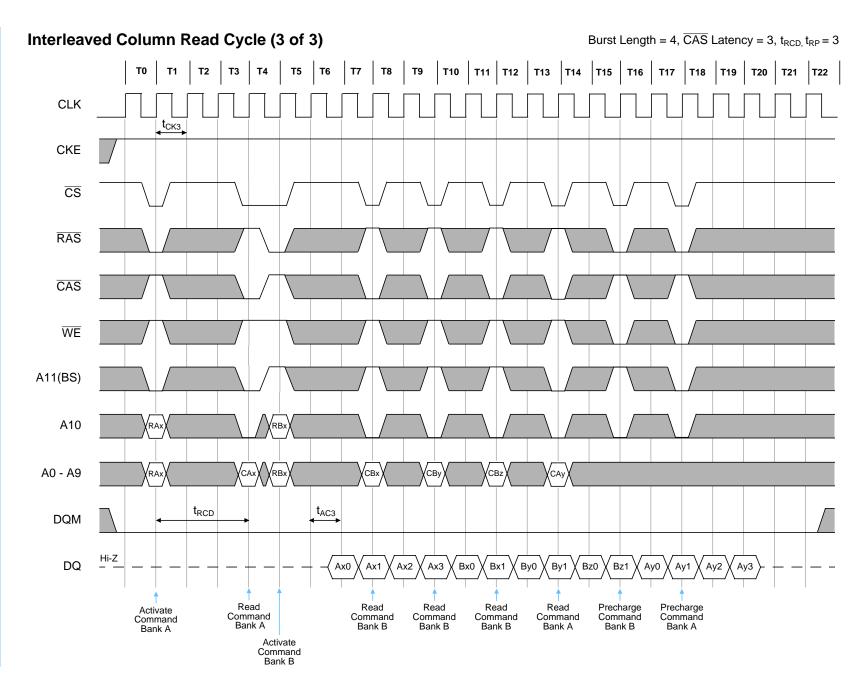

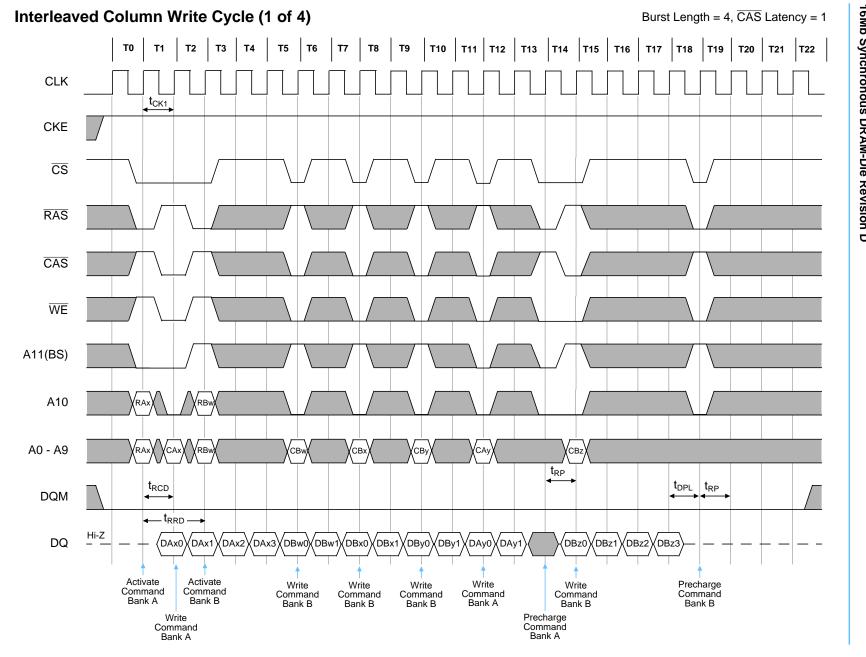

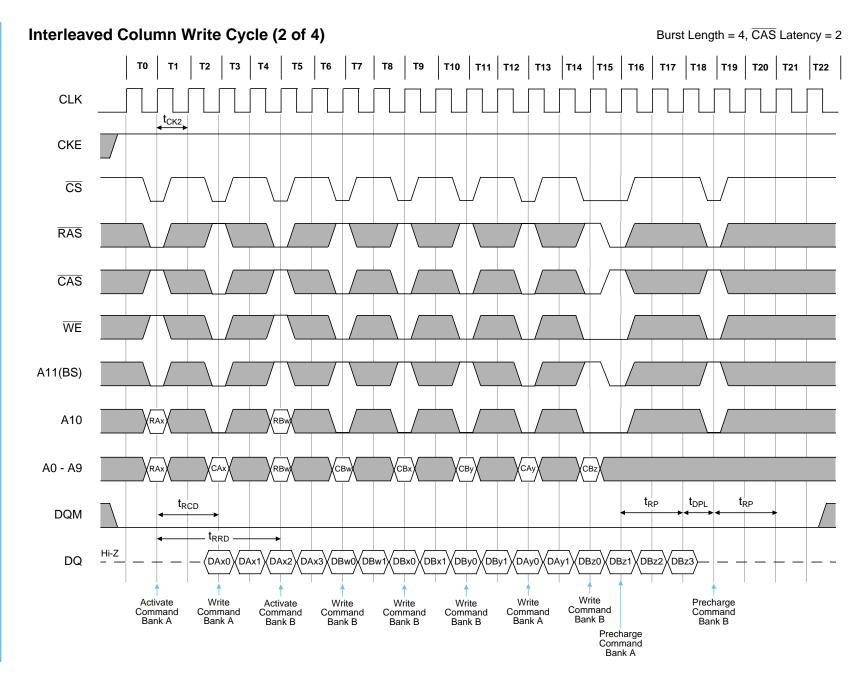

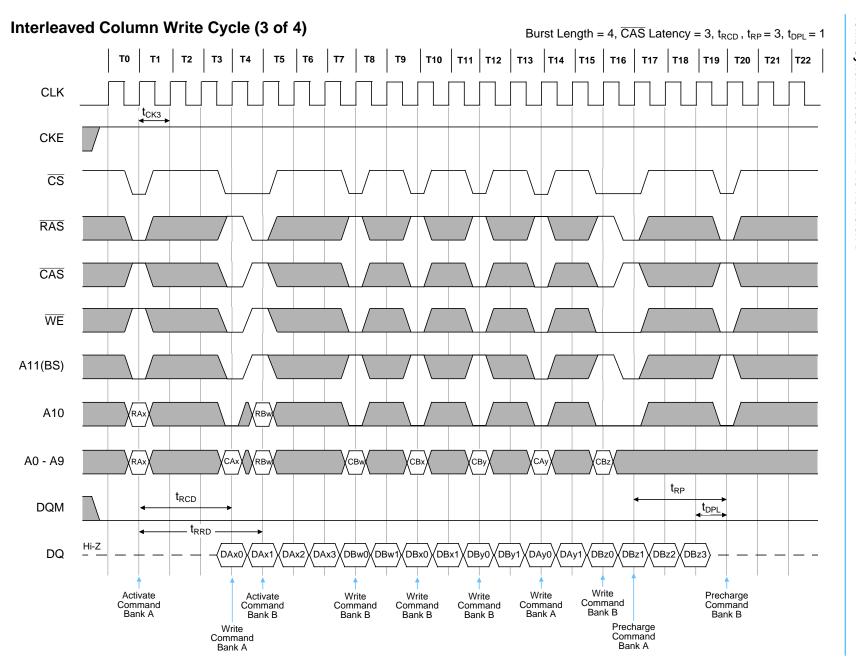

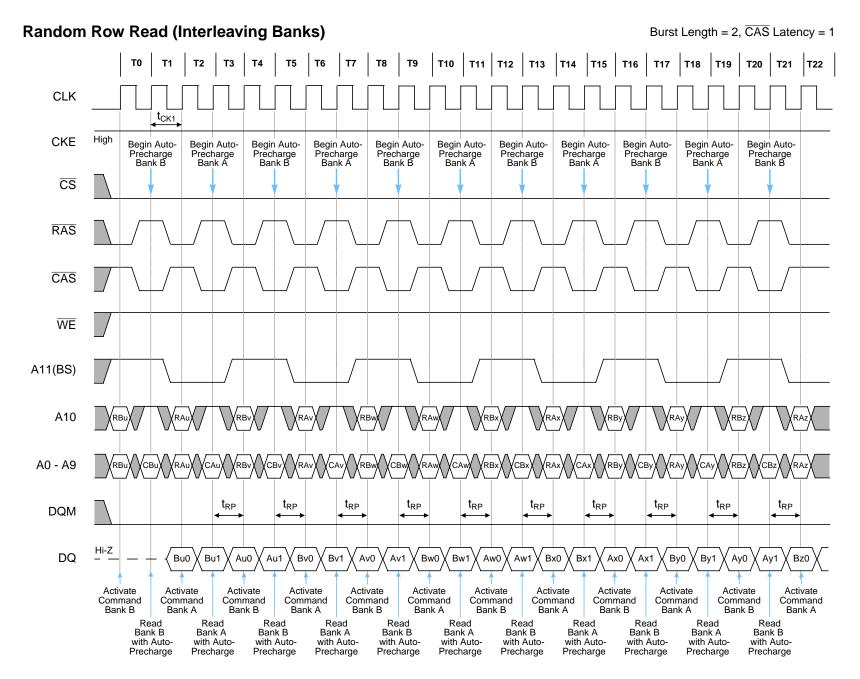

Operating the two memory banks in an interleave fashion allows random access operation to occur at a higher rate than is possible with standard DRAMs. A sequential and gapless data rate of up to 125 MHz is possible depending on burst length, CAS latency, and speed grade of the device.

Auto Refresh (CBR) and Self Refresh (SR) operation are supported. Refreshing both decks of a stacked device simultaneously is allowed during Self Refresh but all other stacked device operations must be performed on a single deck at a time.

## Pin Assignments for Planar Components (Top View)

|             |                 |                      |           |                        |                  |                   |           |                           |                 | 1                 |   |

|-------------|-----------------|----------------------|-----------|------------------------|------------------|-------------------|-----------|---------------------------|-----------------|-------------------|---|

| VDD [       | 1               | 44 🛛 V <sub>SS</sub> | VDD [     | 1                      |                  | ] V <sub>SS</sub> | VDD [     | 1                         | 50              | □ v <sub>ss</sub> |   |

| NC [        | 2               | 43 🛛 NC              | DQ0 [     | 2                      | 43               | ] DQ7             | DQ0 [     | 2                         | 49              | DQ15              |   |

| VSSQ [      | 3               | 42 🛛 VSSC            | Q VSSQ [  | 3                      | 42               | ] VSSC            | ) DQ1 [   | 3                         | 48              | DQ14              |   |

| DQ0 [       | 4               | 41 🛛 DQ3             | DQ1       | 4                      | 41               | ] DQ6             | VSSQ [    | 4                         | 47              | 🖞 vssq            |   |

| VDDQ [      | 5               |                      | VDDQ [    | 5                      | 40               | ] VDDC            | Q DQ2 [   | 5                         | 46              | DQ13              |   |

| NC [        | 6               | 39 🛛 NC              | DQ2       | 6                      | 39               | ] DQ5             | DQ3       | 6                         | 45              | DQ12              |   |

| VSSQ [      | 7               | 38 🛛 VSSC            | Q VSSQ [  | 7                      | 38               | ] VSSC            |           | 7                         | 44              | D VDDQ            | ! |

| DQ1 [       | 8               | 37 🗍 DQ2             | DQ3 [     | 8                      | 37               | ] DQ4             | DQ4 [     | 8                         | 43              | DQ11              |   |

| VDDQ [      | 9               | 36 🛛 VDDO            | ک VDDQ [  | 9                      | 36               | ] VDDC            | Q DQ5 [   | 9                         | 42              | DQ10              |   |

| NC [        | 10              | 35 🗍 NC              | NC [      | 10                     | ) 35             | ] NC              | VSSQ [    | 10                        | ) 41            | 🗅 vssq            |   |

| NC [        | 11              | 34 🛛 NC              | NC [      | 11                     | I 34             | ] NC              | DQ6 [     | 11                        | 40              |                   |   |

| WE          | 12              | 33 🖞 DQM             | WE        | 12                     | 2 33             | ] DQM             | DQ7 [     | 12                        | 2 39            | DQ8               |   |

| CAS         | 13              | 32 🛛 CLK             | CAS [     | 13                     | 3 32             | ] CLK             | VDDQ [    | 13                        | 3 38            | D VDDQ            | ! |

| RAS         | 14              | 31 🛛 СКЕ             | RAS       | 14                     | 1 31             | ] CKE             | LDQM [    | 14                        | 4 37            | лс                |   |

| <u>cs</u> [ | 15              | 30 🛛 NC              |           | 15                     | 5 30             | ] NC              | WE        | 15                        | 5 36            | DUDQN             | 1 |

| A11(BS) [   | 16              | 29 🗋 A9              | A11(BS) [ | 16                     | 3 29             | ] A9              | CAS       | 16                        | 35              | р сгк             |   |

| A10 [       | 17              | 28 🛛 A8              | A10 [     | 17                     | 7 28             | ] A8              | RAS       | 17                        | <b>7</b> 34     | 🛛 СКЕ             |   |

| A0 [        | 18              | 27 🗋 A7              | A0 [      | 18                     | 3 27             | ] A7              | CS [      | 18                        | 3 33            | D NC              |   |

| A1 [        | 19              | 26 🗋 A6              | A1 [      | 19                     | 9 26             | ] A6              | A11(BS) [ | 19                        | 32              | ] A9              |   |

| A2 [        | 20              | 25 🗋 A5              | A2 [      | 20                     | ) 25             | ] A5              | A10 [     | 20                        | ) 31            | ] A8              |   |

| A3 [        | 21              | 24 🛛 A4              | A3 [      | 21                     | I 24             | ] A4              | A0 [      | 21                        | 30              | 🛛 A7              |   |

| VDD [       | 22              | 23 🛛 V <sub>SS</sub> | VDD [     | 22                     | 2 23             | ] V <sub>SS</sub> | A1 [      | 22                        | 2 29            | ] A6              |   |

|             |                 |                      |           | L                      |                  |                   | A2 [      | 23                        | 3 28            | ] A5              |   |

|             |                 |                      |           |                        |                  |                   | A3 [      | 24                        | 4 27            | 🛛 A4              |   |

|             |                 |                      |           |                        |                  |                   | VDD [     | 25                        | 5 26            | □ Vss             |   |

| 44-pin      | Plastic TSOP(I  | l) 400 mil           | 44-pin    | Pla                    | stic TSOP(II) 40 | 0 mil             | 50-pin    | Pla                       | stic TSOP(II) 4 | 00 mil            |   |

| -           | bit x 4 I/O x 2 | -                    | -         | 1Mbit x 8 I/O x 2 Bank |                  |                   | -         | 512Kbit x 16 I/O x 2 Bank |                 |                   |   |

|             |                 |                      |           |                        |                  |                   | 5121      |                           |                 |                   |   |

|             | IBM0316409C     | Г3                   |           | IBN                    | M0316809CT3      |                   |           | IBI                       | M0316169CT3     |                   |   |

## **Pin Description**

| CLK      | Clock Input           | DQ0-DQ15        | Data Input/Output     |

|----------|-----------------------|-----------------|-----------------------|

| CKE      | Clock Enable          | DQM, LDQM, UDQM | Data Mask             |

| CS       | Chip Select           | VDD             | Power (+3.3V)         |

| RAS      | Row Address Strobe    | VSS             | Ground                |

| CAS      | Column Address Strobe | VDDQ            | Power for DQs (+3.3V) |

| WE       | Write Enable          | VSSQ            | Ground for DQs        |

| A11 (BS) | Bank Select           | NC              | No Connection         |

| A0 - A10 | Address Inputs        | _               |                       |

## Pin Assignments for 2-High Stack Package (Dual CS Pins) (Top View)

|          | 1 |    |    | 1 |                 |

|----------|---|----|----|---|-----------------|

| VDD      | С | 1  | 44 | þ | V <sub>SS</sub> |

| NC       | Ц | 2  | 43 | þ | NC              |

| VSSQ     | Ц | 3  | 42 | þ | VSSQ            |

| DQ0      | С | 4  | 41 | þ | DQ3             |

| VDDQ     | С | 5  | 40 | þ | VDDQ            |

| NC       | С | 6  | 39 | þ | NC              |

| VSSQ     | С | 7  | 38 | þ | VSSQ            |

| DQ1      | Ц | 8  | 37 | þ | DQ2             |

| VDDQ     | Ц | 9  | 36 | þ | VDDQ            |

| NC       | Ц | 10 | 35 | þ | NC              |

| NC       | С | 11 | 34 | þ | NC              |

| WE       | С | 12 | 33 | Ь | DQM             |

| CAS      | Ц | 13 | 32 | þ | CLK             |

| RAS      | Ц | 14 | 31 | þ | CKE             |

| * CS0/NC | С | 15 | 30 | þ | NC/CS1 *        |

| A11 (BS) | С | 16 | 29 | þ | A9              |

| A10      | С | 17 | 28 | þ | A8              |

| A0       | С | 18 | 27 | þ | A7              |

| A1       | С | 19 | 26 | þ | A6              |

| A2       | С | 20 | 25 | þ | A5              |

| A3       | Ц | 21 | 24 | þ | A4              |

| VDD      | С | 22 | 23 | þ | V <sub>SS</sub> |

|          |   |    |    |   |                 |

## 44-pin Plastic TSOJ(II) 400 mil (2Mbit x 4 I/O x 2 Bank) x 2 High IBM03164B9CT3

\*  $\overline{CS0}$  selects the lower DRAM in the stack. \*  $\overline{CS1}$  selects the upper DRAM in the stack.

## **Pin Description**

| CLK      | Clock Input           | DQ0-DQ3 | Data Input/Output     |

|----------|-----------------------|---------|-----------------------|

| CKE      | Clock Enable          | DQM     | Data Mask             |

| CS0, CS1 | Chip Select           | VDD     | Power (+3.3V)         |

| RAS      | Row Address Strobe    | VSS     | Ground                |

| CAS      | Column Address Strobe | VDDQ    | Power for DQs (+3.3V) |

| WE       | Write Enable          | VSSQ    | Ground for DQs        |

| A11 (BS) | Bank Select           | NC      | No Connection         |

| A0 - A10 | Address Inputs        | —       |                       |

## Input/Output Functional Description

| Symbol                                                 | Туре            | Signal | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------|-----------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                                                    | Input           | Pulse  | Positive<br>Edge | The system clock input. All of the SDRAM inputs are sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CKE                                                    | Input           | Level  | Active<br>High   | Activates the CLK signal when high and deactivates the CLK signal when low. By deactivating the clock, CKE low initiates the Power Down mode, Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

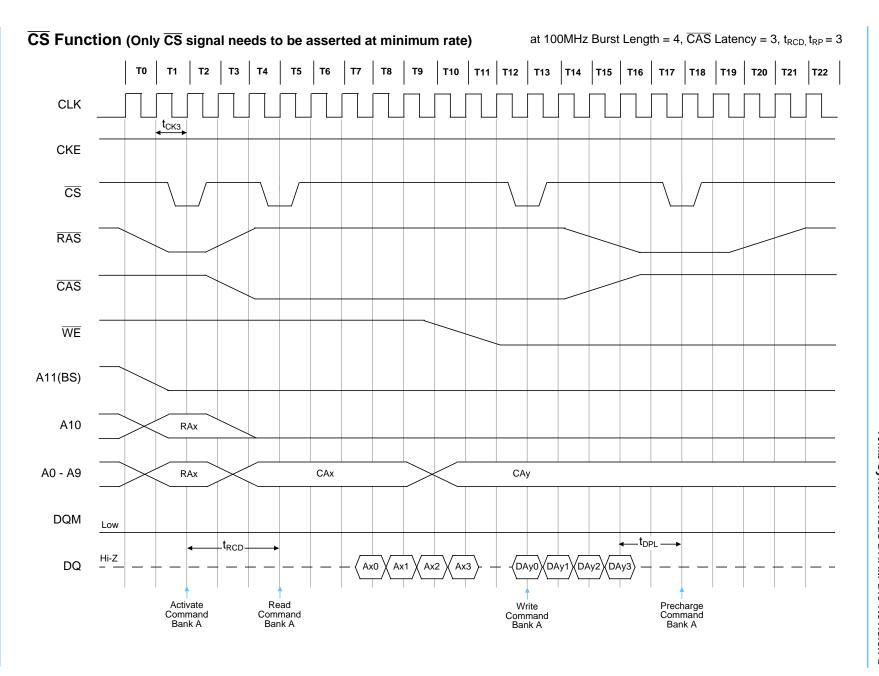

| $\frac{\overline{CS},}{\overline{CS0},\overline{CS1}}$ | Input           | Pulse  | Active Low       | $\overline{\text{CS}}$ ( $\overline{\text{CS0}}$ , $\overline{\text{CS1}}$ for stacked devices) enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $\frac{\overline{RAS}, \overline{CAS}}{\overline{WE}}$ | Input           | Pulse  | Active Low       | When sampled at the positive rising edge of the clock, $\overline{CAS}$ , $\overline{RAS}$ , and $\overline{WE}$ define the operation to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A11 (BS)                                               | Input           | Level  | —                | Selects which bank is to be active. A11 low selects bank A and A11 high selects bank B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A0 - A10                                               | Input           | Level  |                  | <ul> <li>During a Bank Activate command cycle, A0-A10 defines the row address (RA0-RA10) when sampled at the rising clock edge.</li> <li>During a Read or Write command cycle, A0-A9 defines the column address (CA0-CA9) when sampled at the rising clock edge.</li> <li>A10 is used to invoke Auto-Precharge operation. If A10 is high, Auto-Precharge is selected and A11 defines the bank to be precharged (low=bank A, high=bank B). If A10 is low, Auto-Precharge is disabled.</li> <li>During a Precharge command cycle, A10 is used in conjunction with A11 to control which bank(s) to precharge. If A10 is high, both bank A and bank B will be precharged regardless of the state of A11. If A10 is low, then A11 is used to define which bank to precharge.</li> </ul> |

| DQ0 - DQ15                                             | Input<br>Output | Level  | —                | Data Input/Output pins operate in the same manner as on conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

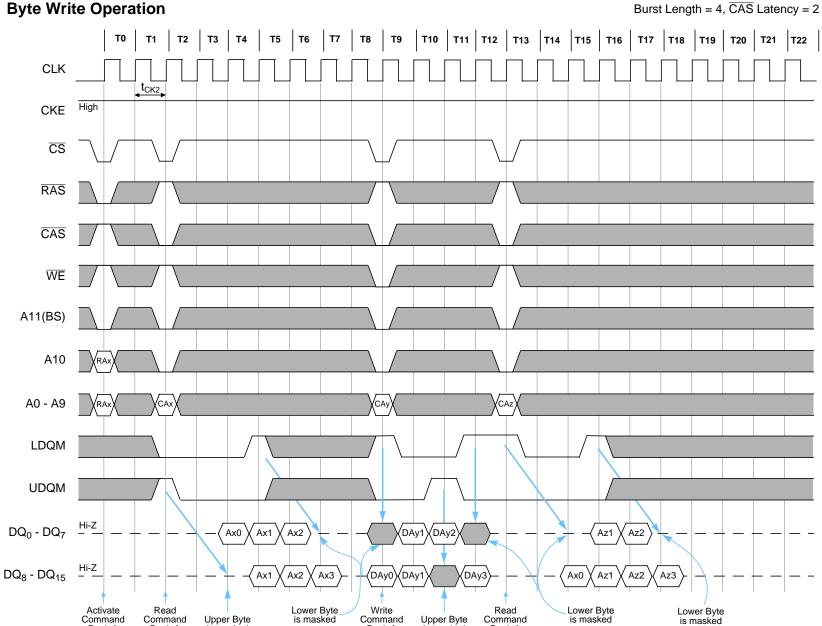

| DQM<br>LDQM<br>UDQM                                    | Input           | Pulse  | Active Low       | The DQ mask (DQM) places the DQ buffers in a high impedance state when sampled high. In Read mode, DQM has a latency of two clock cycles and controls the output buffers consistent with an output enable. In Write mode, DQM has a latency of zero and operates as a word mask by allowing input data to be written if it is low but blocks the write operation if DQM is high.                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDD, V <sub>SS</sub>                                   | Supply          | —      | —                | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VDDQ, VSSQ                                             | Supply          | —      | —                | Isolated power supply and ground for the output buffers to provide improved noise immu-<br>nity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## Ordering Information - Planar Devices (Single CS Pin)

| Part Number        | CAS<br>Latencies | I/O<br>Width | I/O<br>Type | Package                | Power<br>Supply | Clock<br>Cycle |

|--------------------|------------------|--------------|-------------|------------------------|-----------------|----------------|

| IBM0316409CT3D-80  | 2,3              | x4           | LVTTL       | 400mil Type II TSOP-44 | 3.3V            | 8ns            |

| IBM0316409CT3D-10  | 1,2,3            | x4           | LVTTL       | 400mil Type II TSOP-44 | 3.3V            | 10ns           |

| IBM0316809CT3D-80  | 2,3              | x8           | LVTTL       | 400mil Type II TSOP-44 | 3.3V            | 8ns            |

| IBM0316809CT3D-360 | 2,3              | x8           | LVTTL       | 400mil Type II TSOP-44 | 3.3V            | 10ns           |

| IBM0316809CT3D-10  | 1,2,3            | x8           | LVTTL       | 400mil Type II TSOP-44 | 3.3V            | 10ns           |

| IBM0316169CT3D-80  | 2,3              | x16          | LVTTL       | 400mil Type II TSOP-50 | 3.3V            | 8ns            |

| IBM0316169CT3D-10  | 1,2,3            | x16          | LVTTL       | 400mil Type II TSOP-50 | 3.3V            | 10ns           |

# Ordering Information - 2 High Stacked Devices (Dual CS Pins)

| Part Number       | CAS<br>Latencies | I/O<br>Width | I/O<br>Type | Package                       | Power<br>Supply | Clock<br>Cycle |

|-------------------|------------------|--------------|-------------|-------------------------------|-----------------|----------------|

| IBM03164B9CT3D-10 | 1,2,3            | x4           | LVTTL       | 400mil Type II TSOJ-44 2-High | 3.3V            | 10ns           |

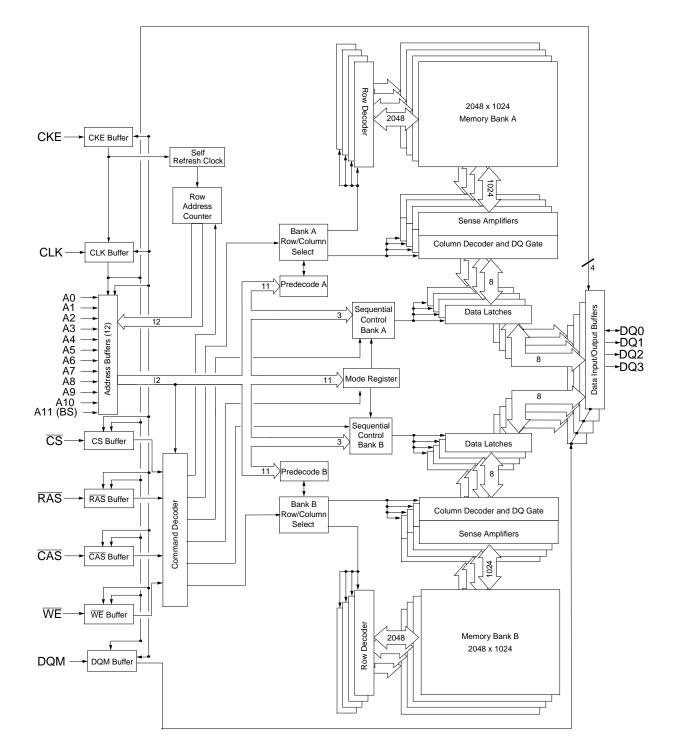

# Block Diagram (2Mbit x 4 I/O x 2 Bank)

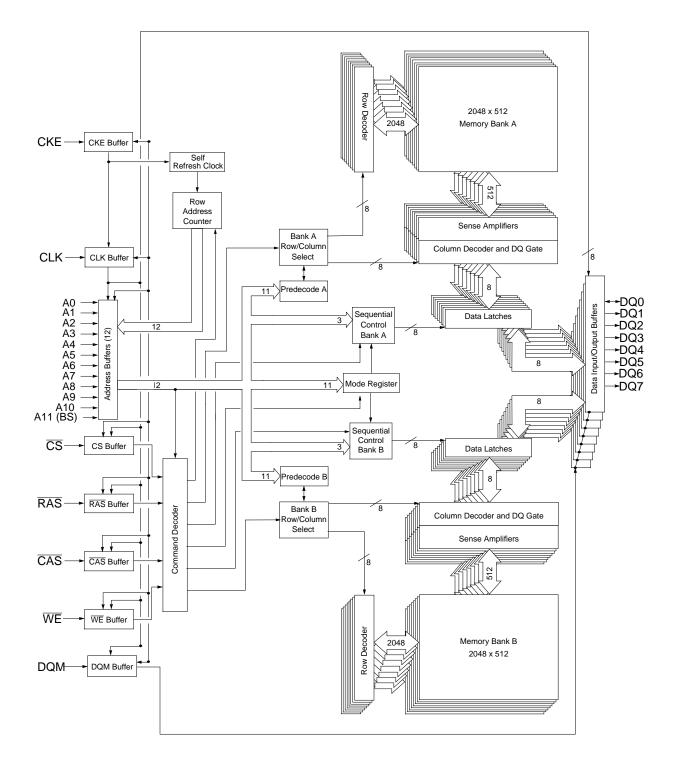

## Block Diagram (1Mbit x 8 I/O x 2 Bank)

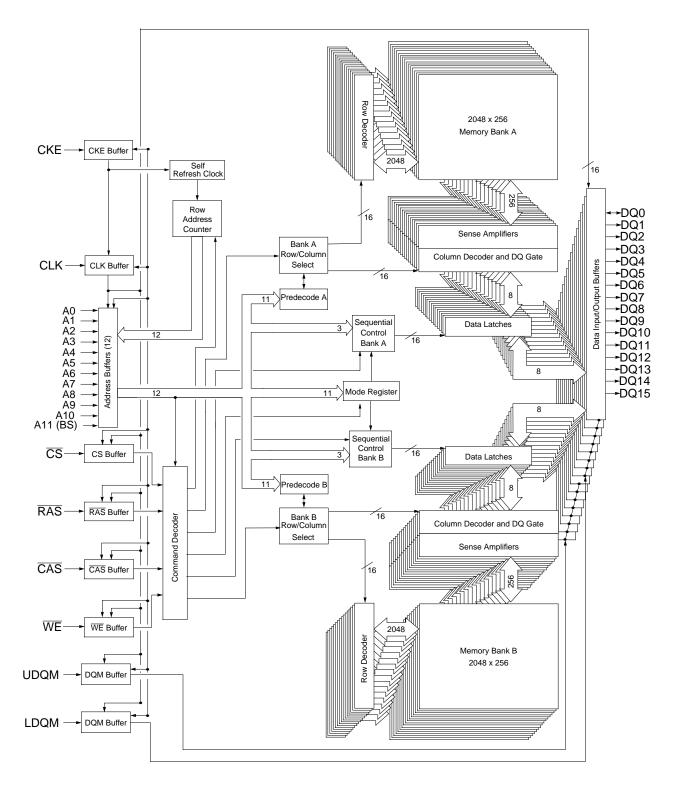

## Block Diagram (512Kbit x 16 I/O x 2 Bank)

## Block Diagram (2Mbit x 4 I/O x 2 Bank) x 2-High

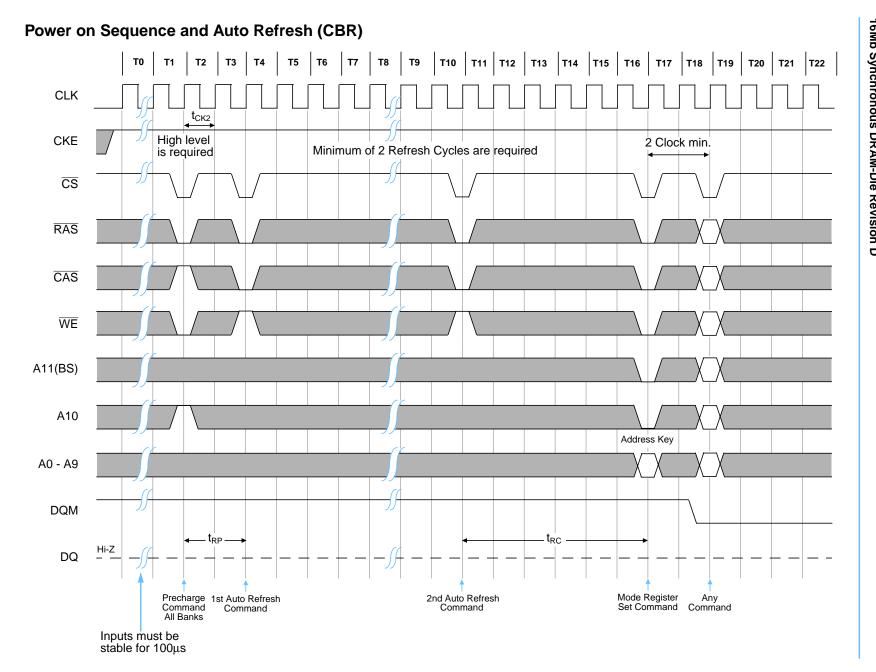

#### Power On and Initialization

The default power on state of the mode register is supplier specific and may be undefined. The following power on and initialization sequence guarantees the device is preconditioned to each user's specific needs.

Like a conventional DRAM, the Synchronous DRAM must be powered up and initialized in a predefined manner. During power on, all VDD and VDDQ pins must be built up simultaneously to the specified voltage no later than any of the input signal voltages. The power on voltage must not exceed VDD+0.3V on any of the input pins or VDD supplies. After power on, an initial pause of 100µs is required followed by a precharge of both banks using the precharge command. To reduce the possibility of data contention on the DQ bus during power on, it is recommended that the DQM pin(s) be held high during the initial pause period. Once both banks have been precharged, a minimum of two Auto Refresh cycles (CBR) must occur before the Mode Register can be programmed. Failure to follow these steps may lead to unpredictable start-up modes.

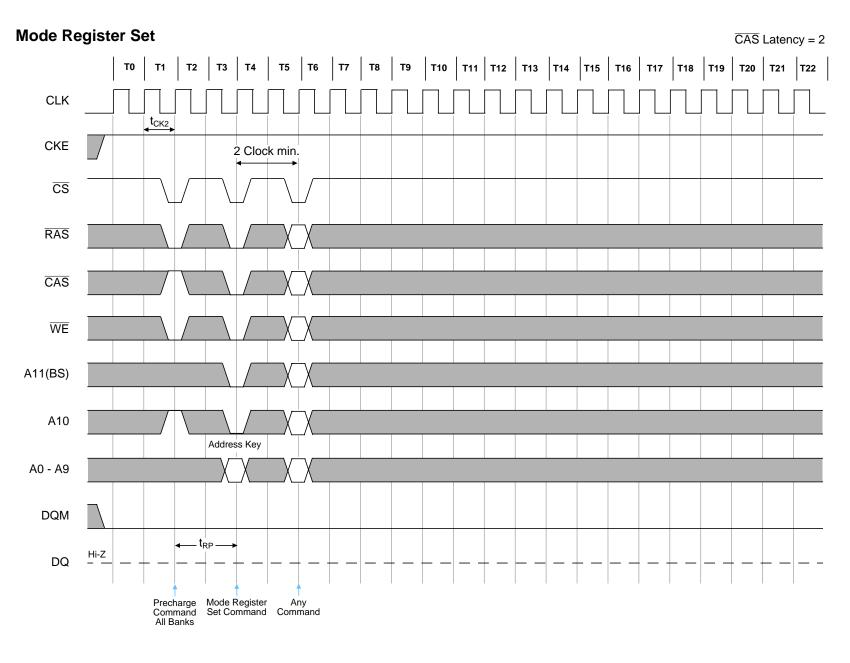

#### **Programming the Mode Register**

For application flexibility, CAS latency, burst length, burst sequence, and operation type are user defined variables and must be programmed into the SDRAM Mode Register with a single Mode Register Set Command. Contents of the Mode Register can be altered by re-executing the Mode Register Set Command. If the user chooses to modify only a subset of the Mode Register variables, all variables must be redefined when the Mode Register Set Command is issued.

After initial power up, the Mode Register Set Command must be issued before read or write cycles may begin. Both banks must be in a precharged state and CKE must be high at least one cycle before the Mode Register Set Command can be issued. The Mode Register Set Command is activated by the low signals of RAS, CAS, CS and WE at the positive edge of the clock. The address input data during this cycle defines the parameters to be set as shown in the Mode Register Operation table. A new command may be issued on the second clock following the mode register set command.

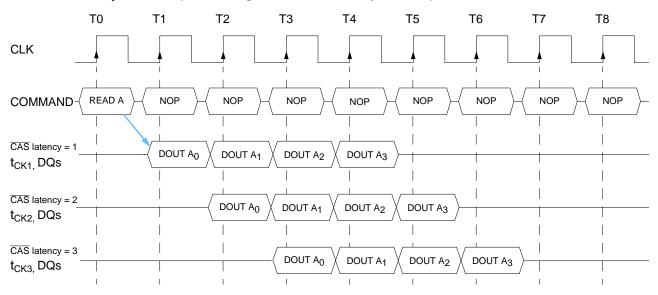

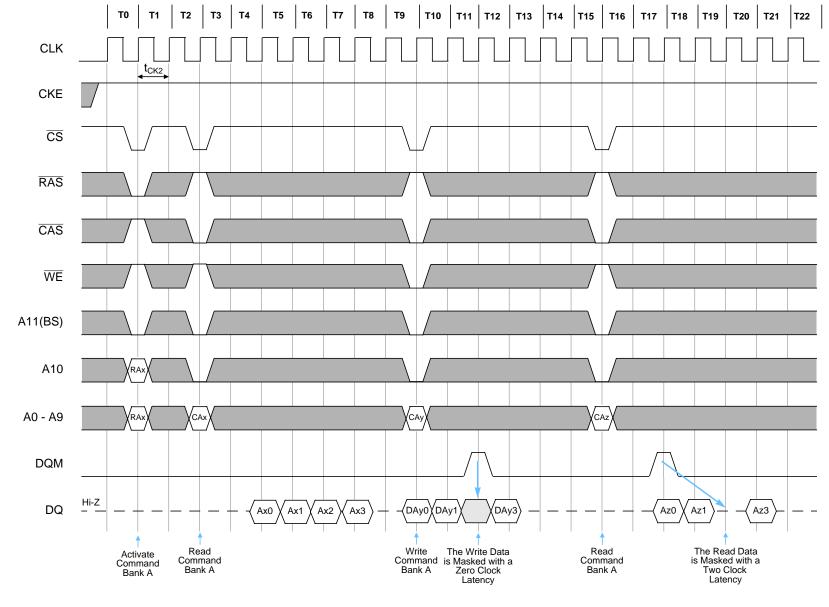

## **CAS** Latency

CAS latency is a parameter that is used to define the delay from when a Read Command is registered on a rising clock edge to when the data from that Read Command becomes available at the outputs. CAS latency is expressed in terms of clock cycles and can be programmed to a value of 1, 2, or 3 cycles. The value of CAS latency is determined by the speed grade of the device and the clock frequency that is used in the application. A table showing the relationship between the CAS latency, speed grade, and clock frequency appears in the Electrical Characteristics section of this document. Once the appropriate CAS latency has been selected it must be programmed into the mode register after power up. For an explanation of this procedure, see Programming the Mode Register in the previous section.

## Mode Register Operation (Address Input For Mode Set)

| M6 | M5 | M4 | Latency  |

|----|----|----|----------|

| 0  | 0  | 0  | Reserved |

| 0  | 0  | 1  | 1        |

| 0  | 1  | 0  | 2        |

| 0  | 1  | 1  | 3        |

| 1  | 0  | 0  | Reserved |

| 1  | 0  | 1  | Reserved |

| 1  | 1  | 0  | Reserved |

| 1  | 1  | 1  | Reserved |

## **Burst Length**

| мо | M1 M0 |      | Length     |            |  |

|----|-------|------|------------|------------|--|

| M2 | IVIT  | IVIU | Sequential | Interleave |  |

| 0  | 0     | 0    | 1          | 1          |  |

| 0  | 0     | 1    | 2          | 2          |  |

| 0  | 1     | 0    | 4          | 4          |  |

| 0  | 1     | 1    | 8          | 8          |  |

| 1  | 0     | 0    | Reserved   | Reserved   |  |

| 1  | 0     | 1    | Reserved   | Reserved   |  |

| 1  | 1     | 0    | Reserved   | Reserved   |  |

| 1  | 1     | 1    | Full Page  | Reserved   |  |

## Burst Mode Operation

Burst mode operation is used to provide a constant flow of data to memory locations (write cycle), or from memory locations (read cycle). There are three parameters that define how the burst mode will operate. These parameters include burst sequence, burst length, and operation mode. The burst sequence and burst length are programmable, and are determined by address bits A0 - A3 during the Mode Register Set command. Operation mode is also programmable and is set by address bits A7 - A10 and BS.

The burst type is used to define the order in which the burst data will be delivered or stored to the SDRAM. Two types of burst sequences are supported, sequential and interleaved. See Table.

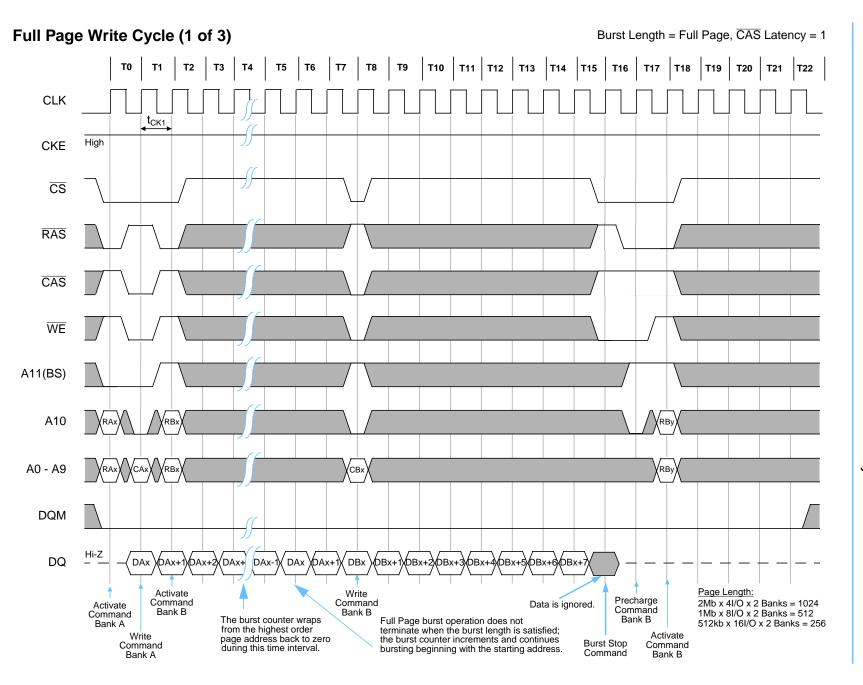

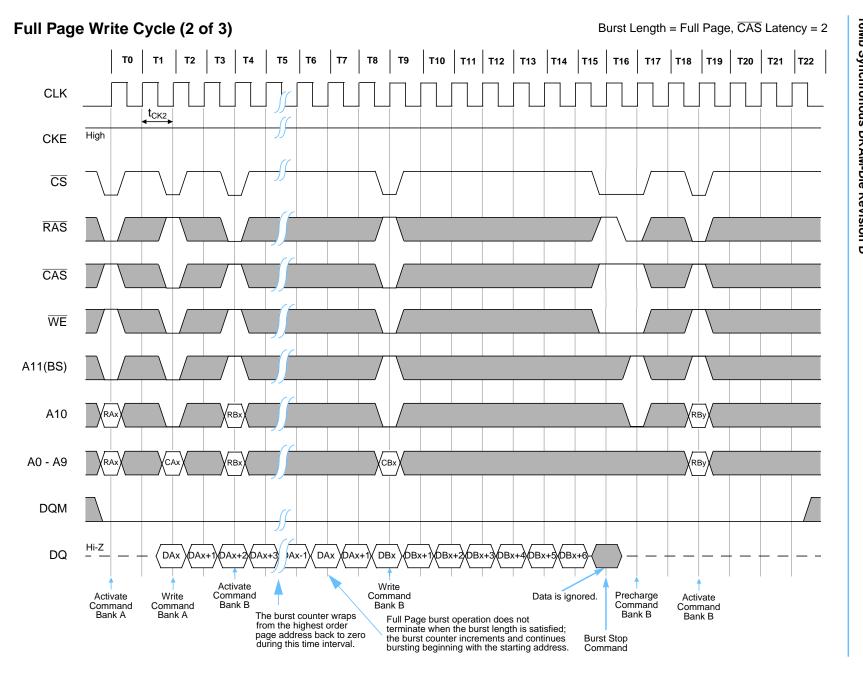

The burst length controls the number of bits that will be output after a Read Command, or the number of bits to be input after a Write Command. The burst length can be programmed to have values of 1, 2, 4, 8 or full page (actual page length is dependent on organization: x4, x8, or x16). Full page burst operation is only possible using the sequential burst type.

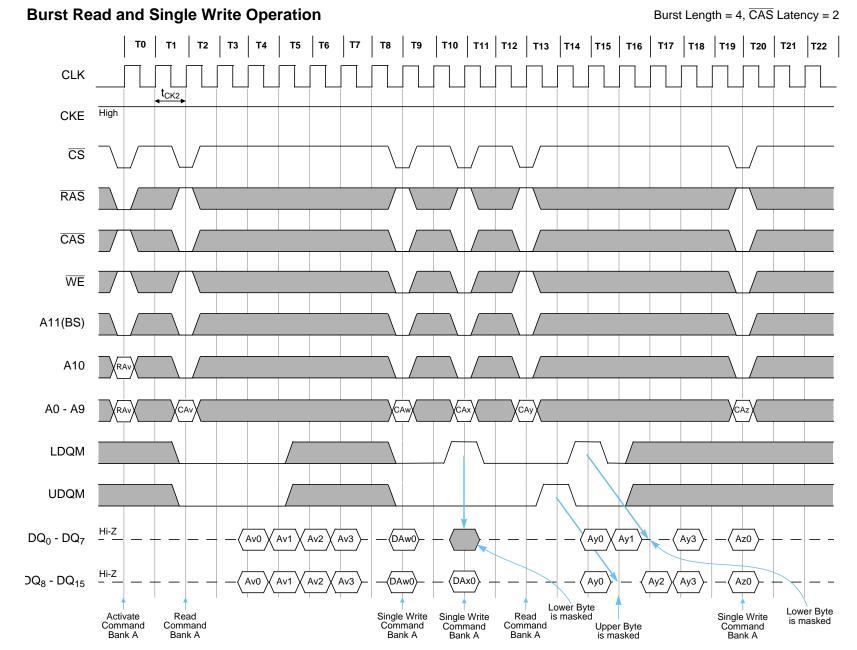

Burst operation mode can be normal operation or multiple burst with single write operation. Normal operation implies that the device will perform burst operations on both read and write cycles until the desired burst length is satisfied. Multiple burst with single write operation was added to support Write Through Cache operation. Here, the programmed burst length only applies to read cycles. All write cycles are single write operations when this mode is selected.

| Burst Length     | Starting Address (A2 A1 A0) | Sequential Addressing (decimal) | Interleave Addressing (decimal) |

|------------------|-----------------------------|---------------------------------|---------------------------------|

| 2                | x x 0                       | 0, 1                            | 0, 1                            |

| 2                | x x 1                       | 1, 0                            | 1, 0                            |

|                  | x 0 0                       | 0, 1, 2, 3                      | 0, 1, 2, 3                      |

| 4                | x 0 1                       | 1, 2, 3, 0                      | 1, 0, 3, 2                      |

| 4                | x 1 0                       | 2, 3, 0, 1                      | 2, 3, 0, 1                      |

|                  | x 1 1                       | 3, 0, 1, 2                      | 3, 2, 1, 0                      |

|                  | 000                         | 0, 1, 2, 3, 4, 5, 6, 7          | 0, 1, 2, 3, 4, 5, 6, 7          |

|                  | 0 0 1                       | 1, 2, 3, 4, 5, 6, 7, 0          | 1, 0, 3, 2, 5, 4, 7, 6          |

|                  | 010                         | 2, 3, 4, 5, 6, 7, 0, 1          | 2, 3, 0, 1, 6, 7, 4, 5          |

| 8                | 011                         | 3, 4, 5, 6, 7, 0, 1, 2          | 3, 2, 1, 0, 7, 6, 5, 4          |

| o                | 100                         | 4, 5, 6, 7, 0, 1, 2, 3          | 4, 5, 6, 7, 0, 1, 2, 3          |

|                  | 101                         | 5, 6, 7, 0, 1, 2, 3, 4          | 5, 4, 7, 6, 1, 0, 3, 2          |

|                  | 110                         | 6, 7, 0, 1, 2, 3, 4, 5          | 6, 7, 4, 5, 2, 3, 0, 1          |

|                  | 111                         | 7, 0, 1, 2, 3, 4, 5, 6          | 7, 6, 5, 4, 3, 2, 1, 0          |

| Full Page (Note) | nnn                         | Cn, Cn+1, Cn+2,                 | Not Supported                   |

## Burst Length and Sequence

Note: Page length is a function of I/O organization and column addressing.

x4 organization (CA0-CA9); Page Length = 1024 bits

x8 organization (CA0-CA8); Page Length = 512 bits

x16 organization (CA0-CA7); Page Length = 256 bits

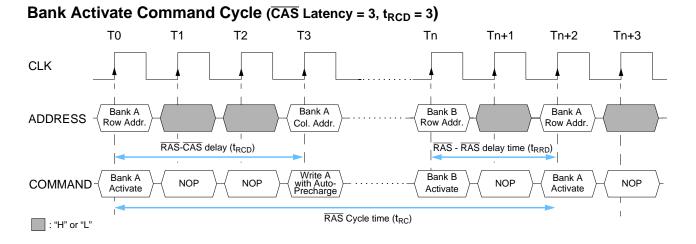

## Bank Activate Command

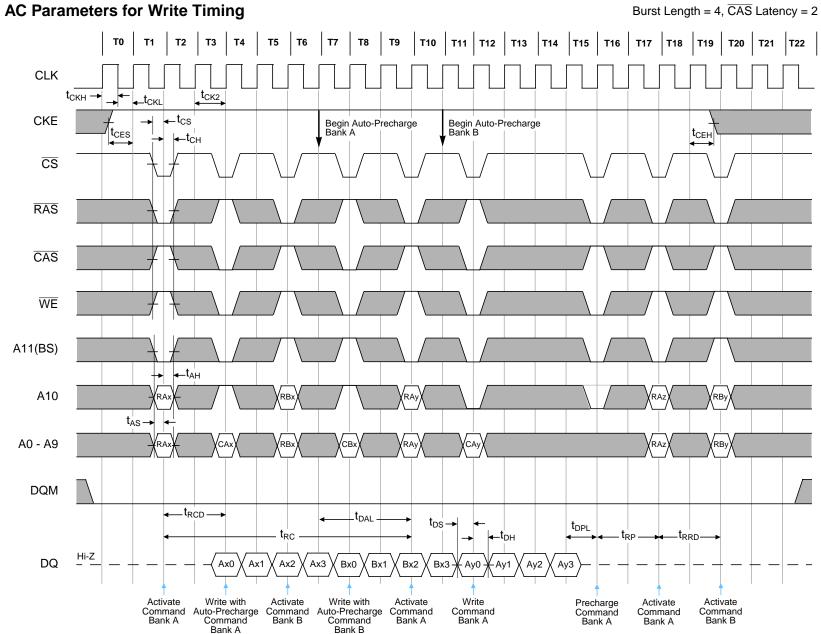

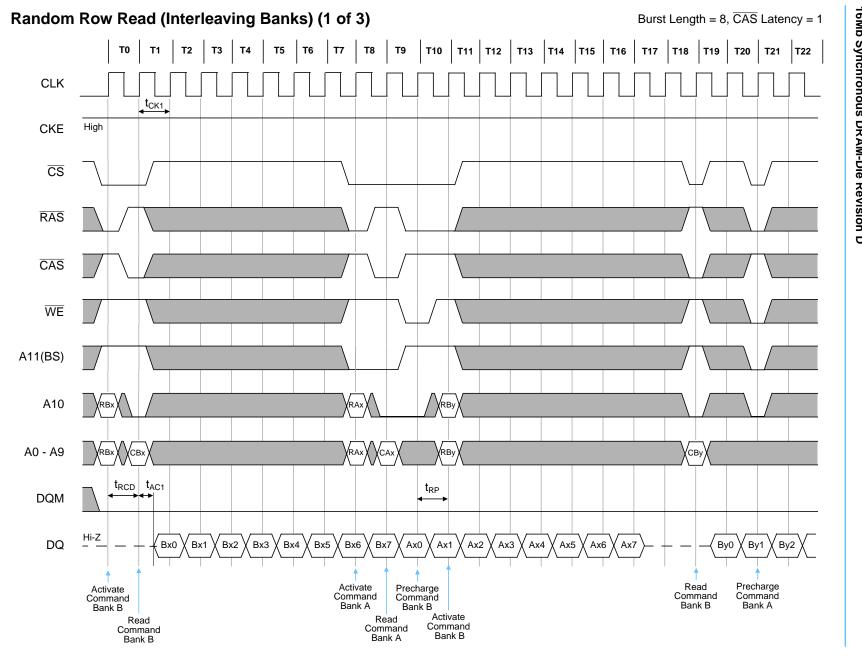

In relation to the operation of a fast page mode DRAM, the Bank Activate command corresponds to a falling RAS signal. The Bank Activate command is issued by holding  $\overline{CAS}$  and  $\overline{WE}$  high with  $\overline{CS}$  and  $\overline{RAS}$  low at the rising edge of the clock. The bank select address, A11 (sometimes referred to as BS), is used to select the desired bank. If BS is low then bank A is activated, if BS is high then bank B is activated. The row address A0 - A10 is used to determine which row to activate in the selected bank. Only banks A and B within a single deck of a 2-High stacked device can be accessed. Simultaneous operation of both decks in a stacked device is not allowed, except during Self Refresh.

The Bank Activate command must be applied before any Read or Write operation can be executed. The delay from when the Bank Activate command is applied to when the first read or write operation can begin must meet or exceed the RAS to CAS delay time ( $t_{RCD}$ ). Once a bank has been activated it must be precharged before another Bank Activate command can be applied to the same bank. The minimum time interval between successive Bank Activate commands to the same bank is determined by the RAS cycle time of the device ( $t_{RC}$ ). The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay time ( $t_{RRD}$ ).

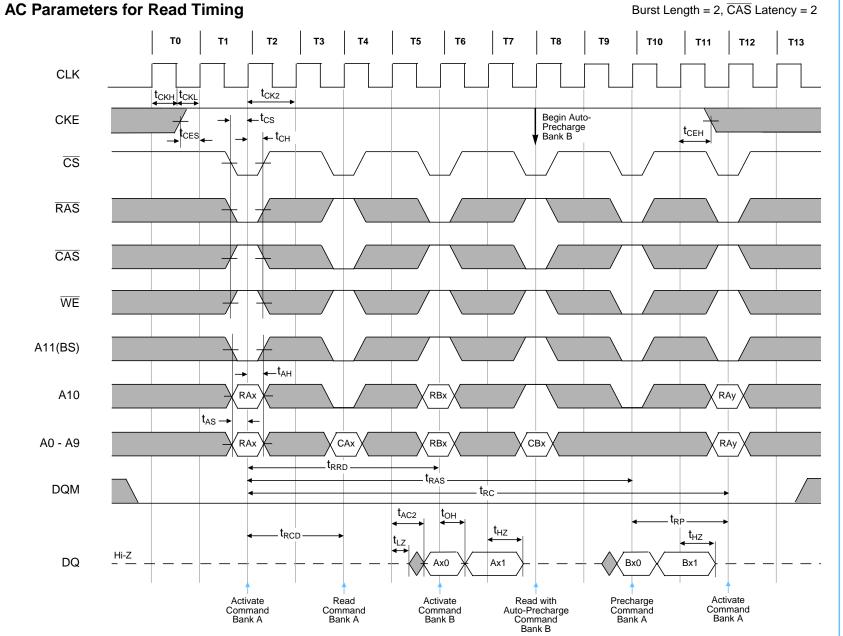

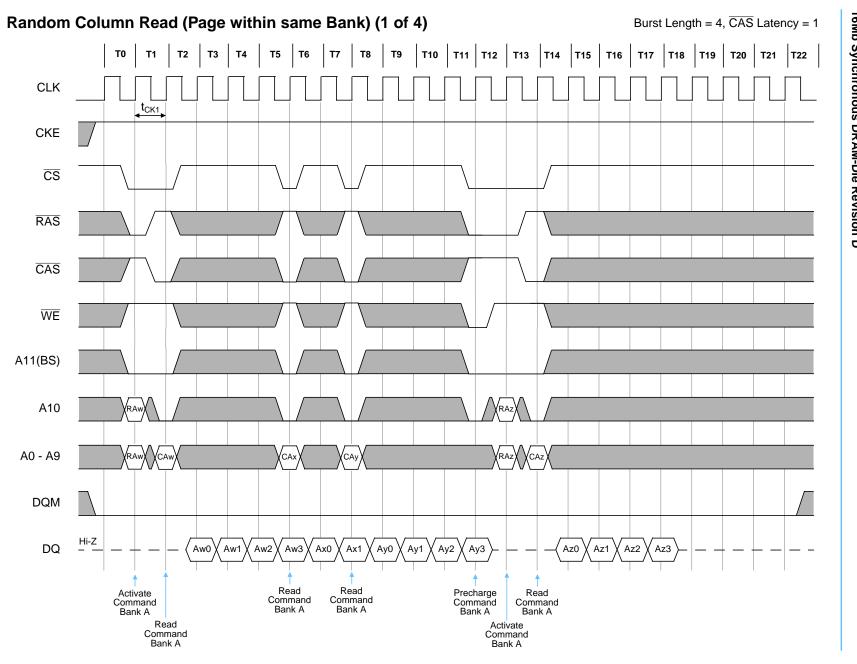

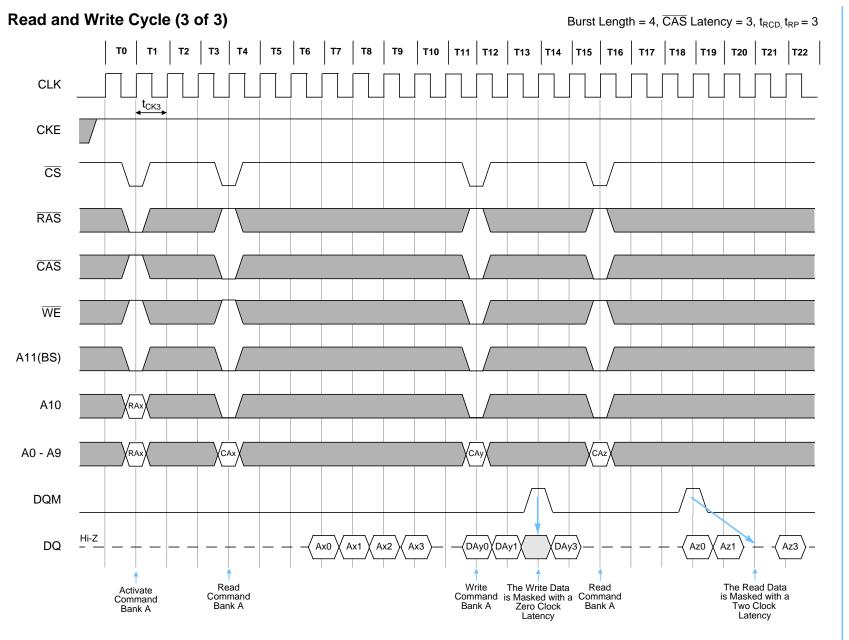

#### Read and Write Access Modes

After a bank has been activated, a read or write cycle can be executed. This is accomplished by setting  $\overline{RAS}$  high and  $\overline{CAS}$  low at the clock's rising edge after the necessary  $\overline{RAS}$  to  $\overline{CAS}$  delay (t<sub>RCD</sub>). WE must also be defined at this time to determine whether the access cycle is a read operation ( $\overline{WE}$  high), or a write operation ( $\overline{WE}$  low).

The SDRAM provides a wide variety of fast access modes. A single Read or Write Command will initiate a serial read or write operation on successive clock cycles at data rates of up to 125 MHz. The number of serial data bits for each access is equal to the burst length, which is programmed into the Mode Register. Although the burst length is user programmable, the boundary of the burst cycle is restricted to specific segments of the page length.

For example, the 2Mbit x 4 I/O x 2 Bank device has a page length of 1024 bits (defined by CA0-CA9). If a burst length of 4 is programmed into the Mode Register, then the page length is divided into 256 uniquely addressable boundary segments (4-bits each). A 4-bit burst operation will occur entirely from one of the 256 groups beginning with the column address supplied to the device during the Read or Write Command (CA0-CA9). The second, third, and fourth access will also occur within this group segment, however, the burst order is a function of the starting address, the burst sequence, and burst boundary.

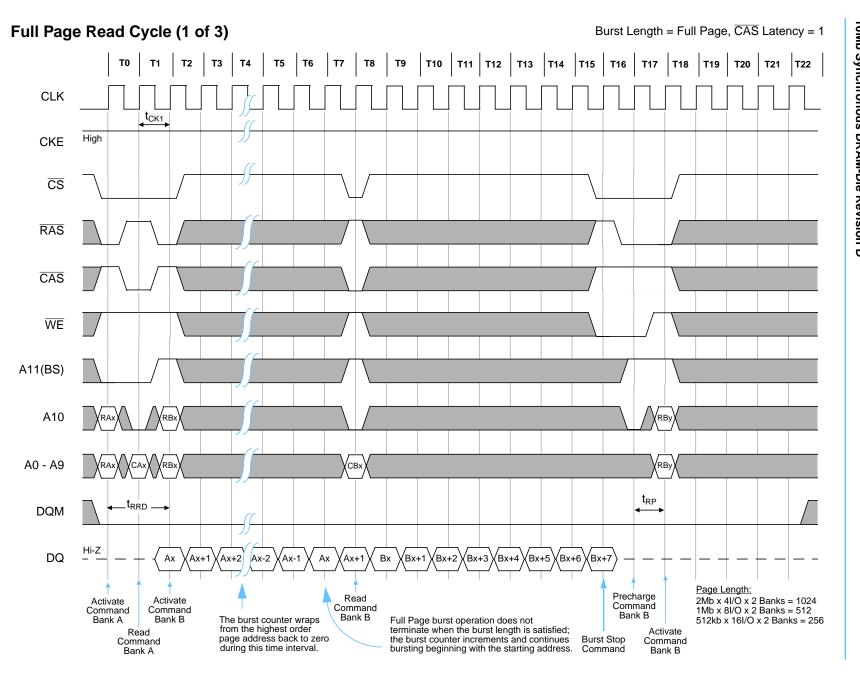

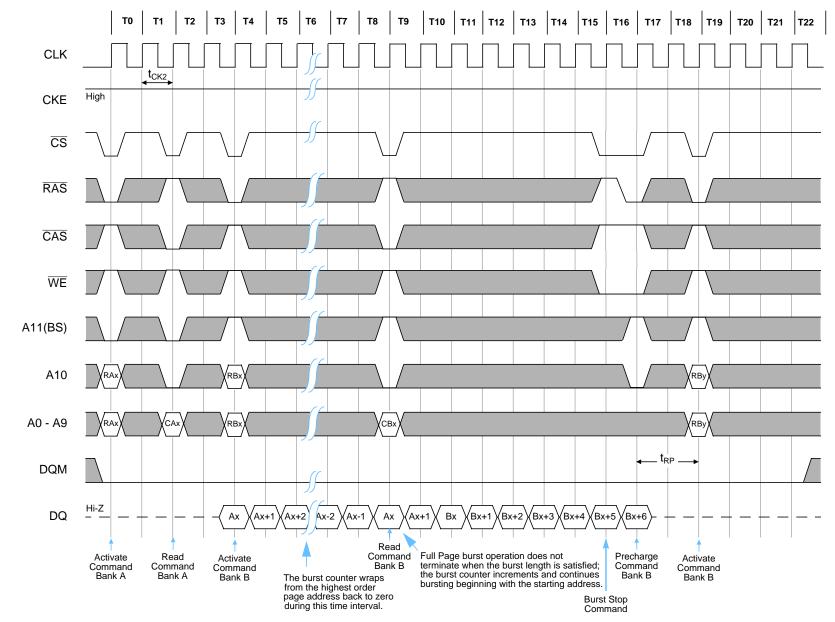

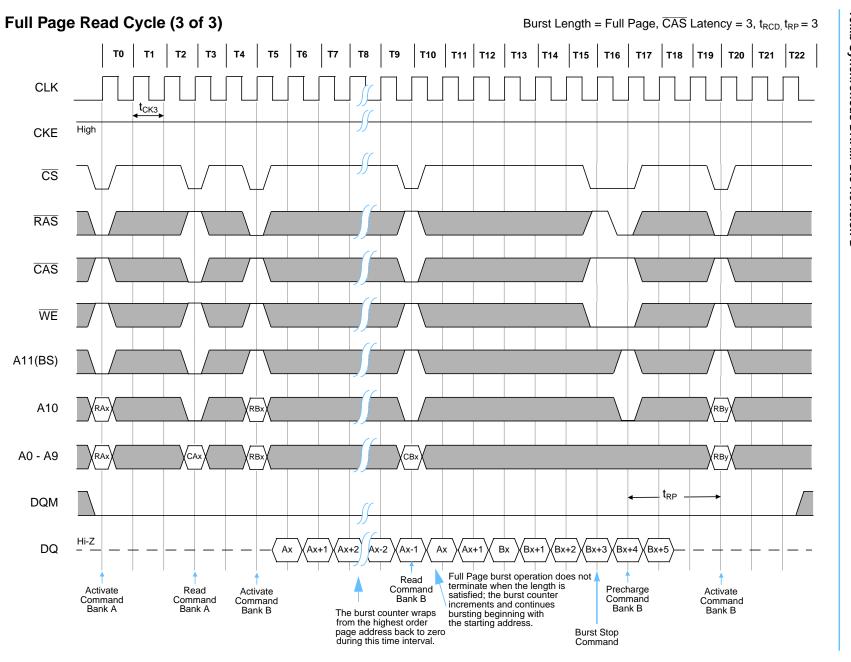

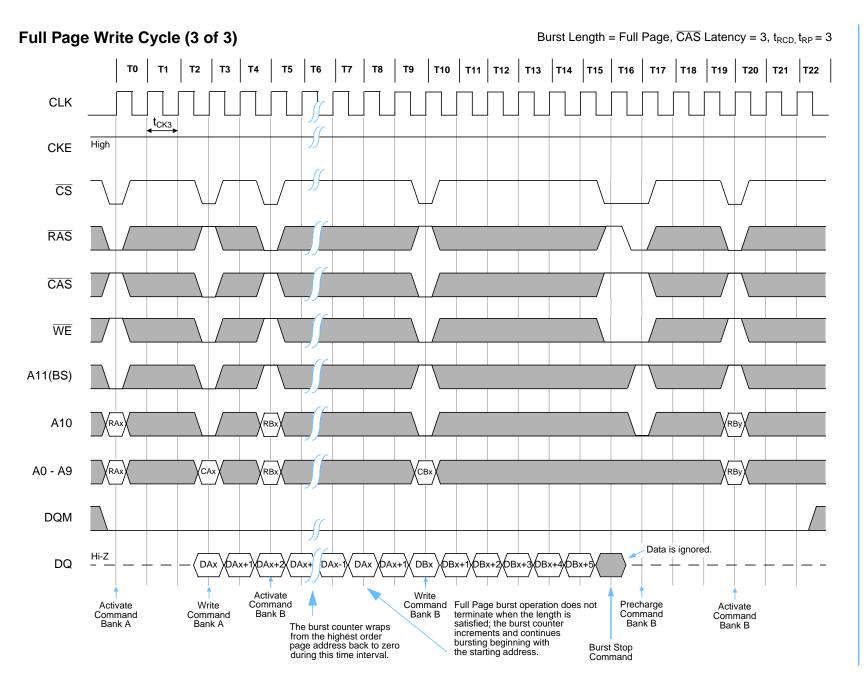

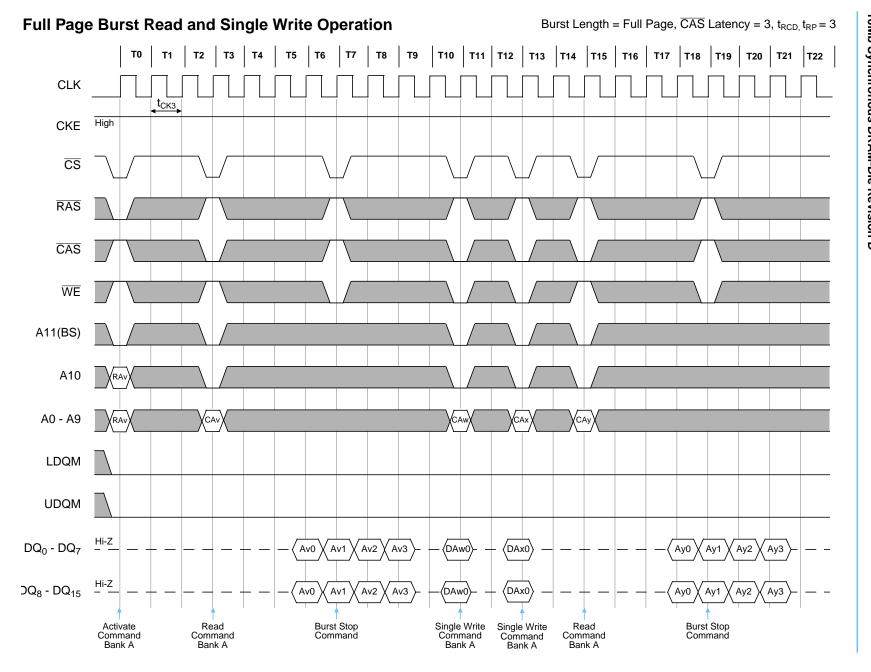

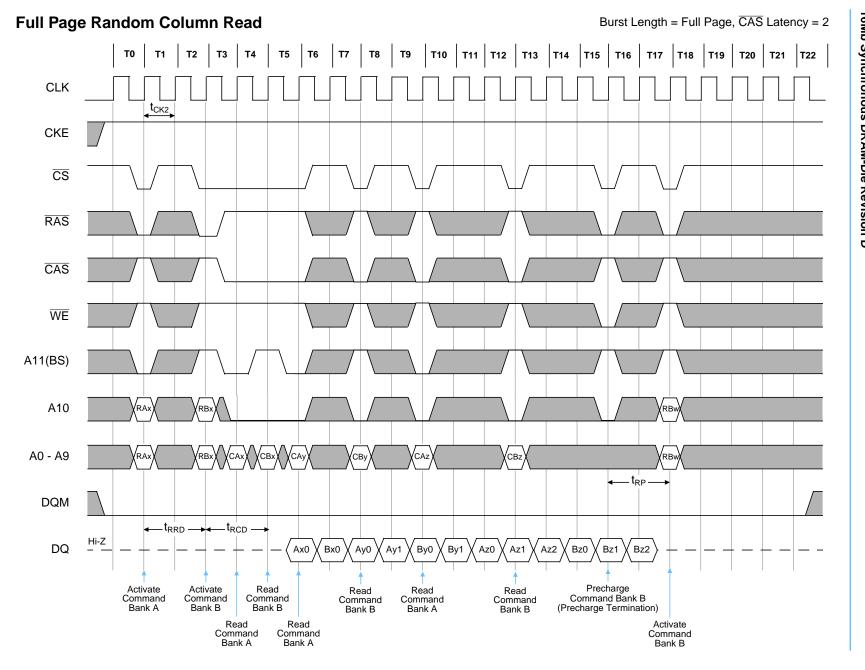

The above discussion does not apply when full page burst is programmed into the Mode Register. Full page burst operation is only allowed for the sequential burst sequence and has no address boundaries. The SDRAM device will continue bursting data even after all locations of the page have been accessed. The burst sequence will start at the column address defined during the read or write cycle and will increment sequentially until the highest order column address has been reached. At this point, the burst counter will reset to address 0 and continue to perform burst read or burst write operations sequentially until either a Burst Stop Command is issued, a Precharge Command is issued to the bursting bank, or until a new Read or Write Command is issued.

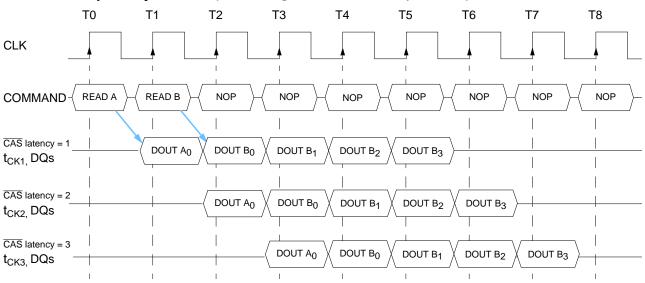

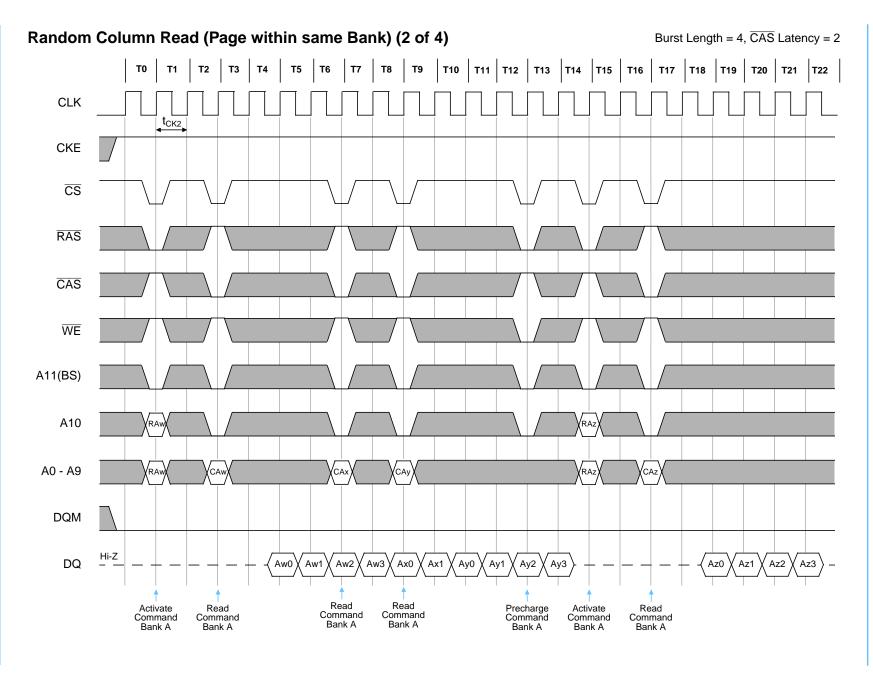

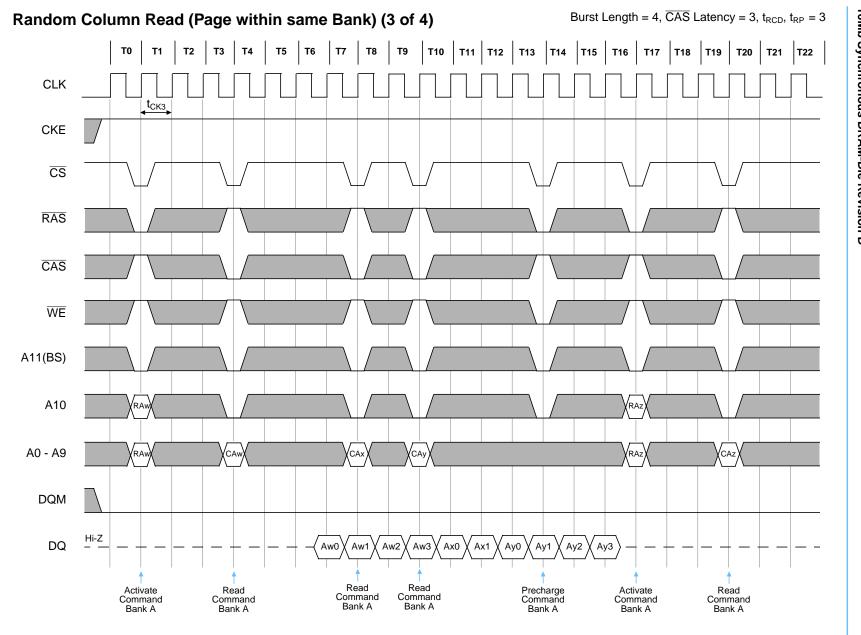

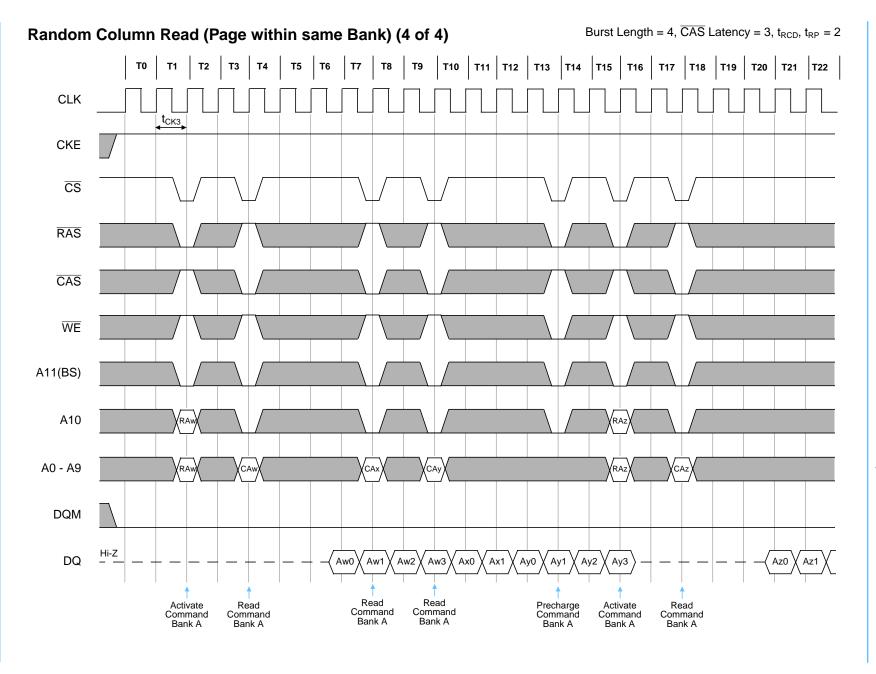

Similar to Page Mode of conventional DRAMs, a read or write cycle can not begin until the sense amplifiers latch the selected row address information. The refresh period ( $t_{REF}$ ) is what limits the number of random column accesses to an activated bank. A new burst access can be done even before the previous burst ends. The ability to interrupt a burst operation at every clock cycle is supported, this is referred to as the 1-N rule. When the previous burst is interrupted by another Read or Write Command, the remaining addresses are overridden by the new address once the CAS Latency has been satisfied.

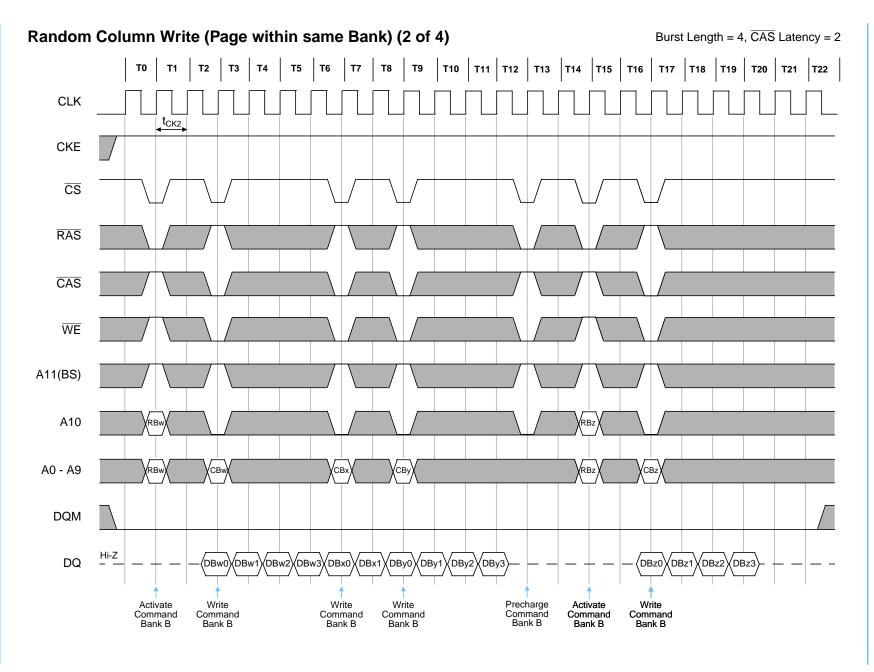

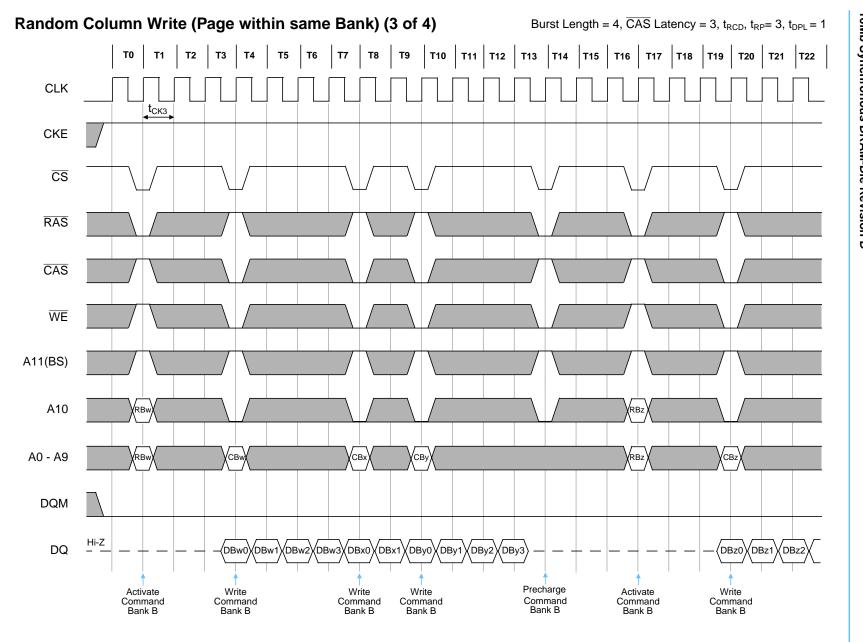

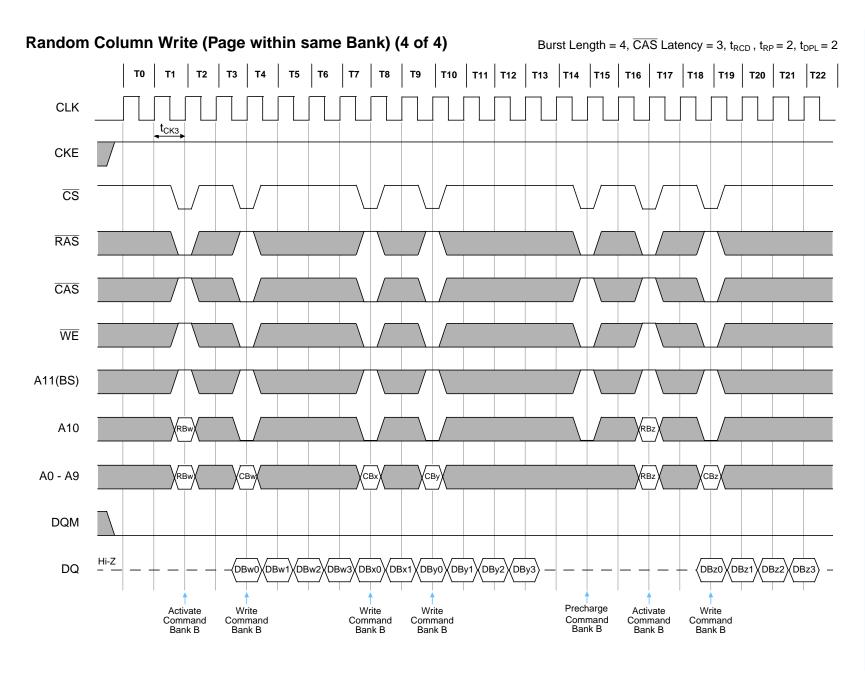

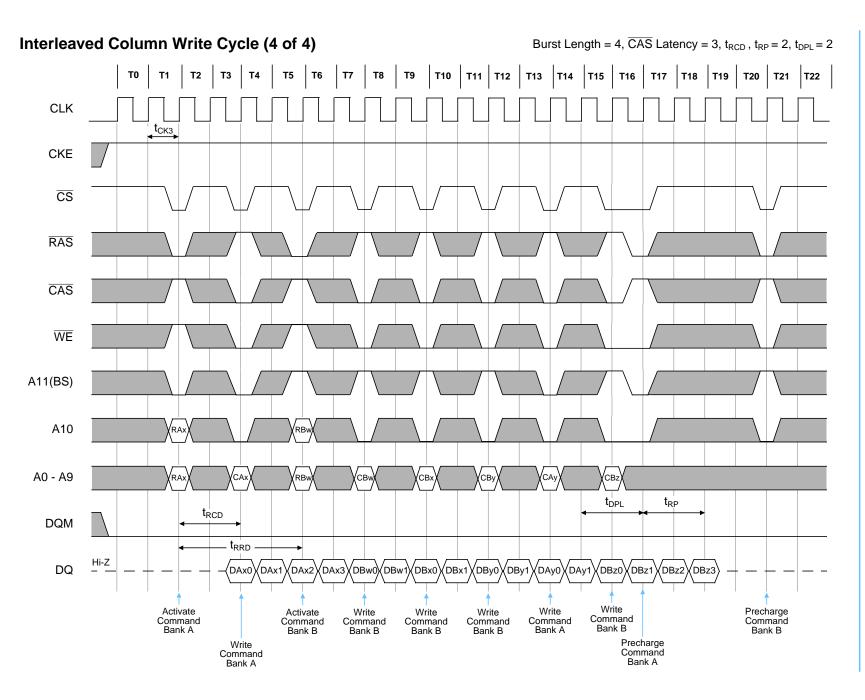

Precharging an active bank after each read or write operation is not necessary providing the same row is to be accessed again. To perform a read or write cycle to a different row within an activated bank, the bank must be precharged and a new Bank Activate command must be issued. When both Bank A and Bank B are activated, interleaved (ping pong) bank Read or Write operations are possible. By using the programmed burst length and alternating the access and precharge operations between the two banks, fast and seamless data access operation among many different pages can be realized. When the two banks are activated, column to column interleave operation can be done between two different pages. Finally, Read or Write Commands can be issued to the same bank or between active banks on every clock cycle.

## **Burst Read Command**

The Burst Read command is initiated by having  $\overline{CS}$  and  $\overline{CAS}$  low while holding  $\overline{RAS}$  and  $\overline{WE}$  high at the rising edge of the clock. The address inputs determine the starting column address for the burst, the Mode Register sets type of burst (sequential or interleave) and the burst length (1, 2, 4, 8, full page). The delay from the start of the command to when the data from the first cell appears on the outputs is equal to the value of the  $\overline{CAS}$  latency that is set in the Mode Register.

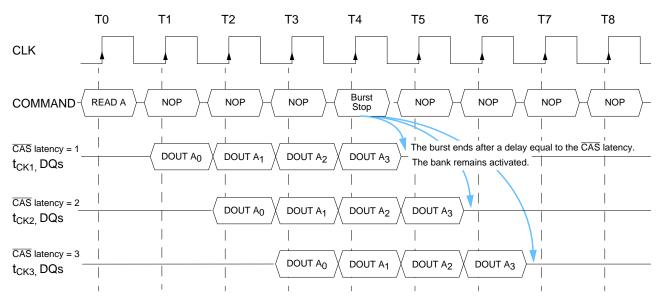

#### **Burst Read Operation** (Burst Length = 4, <u>CAS</u> Latency = 1, 2, 3)

#### Read Interrupted by a Read

A Burst Read may be interrupted before completion of the burst by another Read Command, with the only restriction being that the interval that separates the commands must be at least one clock cycle. When a burst read operation is interrupted, the remaining addresses of the current burst cycle are overridden starting with the new column address applied with the interrupting Read Command. The data from the first Read Command continues to appear on the DQs until the CAS latency of the interrupting Read Command is satisfied. At this point, the data from the interrupting Read Command will appear on the DQs and continue for the full burst length.

#### Read Interrupted by a Read (Burst Length = 4, CAS Latency = 1, 2, 3)

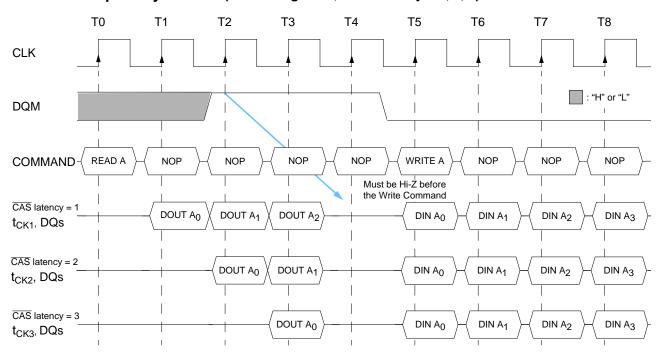

## Read Interrupted by a Write

To interrupt a burst read with a Write Command, DQM must be used to avoid data contention on the data bus by placing the chip output drivers in a high impedance state at least one clock cycle before the Write Command is initiated. To insure the chip output drivers are tri-stated one cycle before the write operation begins, DQM must be activated at least 3 clock cycles before the Write Command and be deactivated in the same clock cycle as the Write Command.

#### Read Interrupted by a Write (Burst Length = 4, $\overline{CAS}$ Latency = 1, 2, 3)

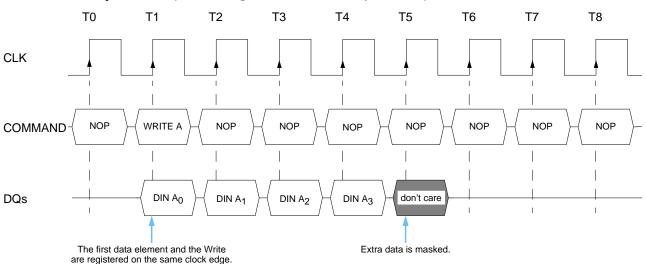

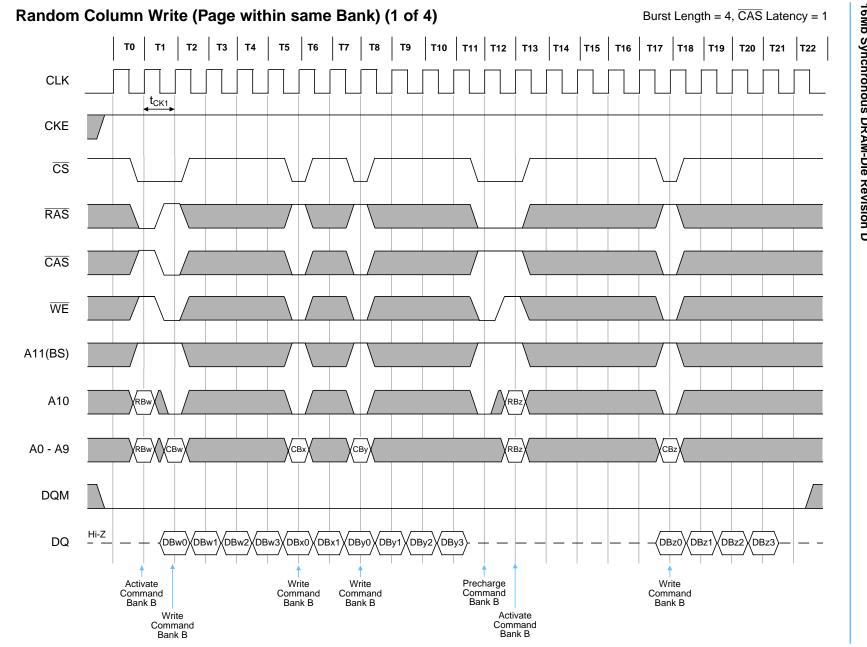

#### Burst Write Command

The Burst Write command is initiated by having  $\overline{CS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  low while holding  $\overline{RAS}$  high at the rising edge of the clock. The address inputs determine the starting column address. There is no  $\overline{CAS}$  latency required for burst write cycles. Data for the first burst write cycle must be applied on the DQ pins on the same clock cycle that the Write Command is issued. The remaining data inputs must be supplied on each subsequent rising clock edge until the burst length is completed. When the burst has finished, any additional data supplied to the DQ pins will be ignored.

#### Burst Write Operation (Burst Length = 4, CAS Latency = 1, 2, 3)

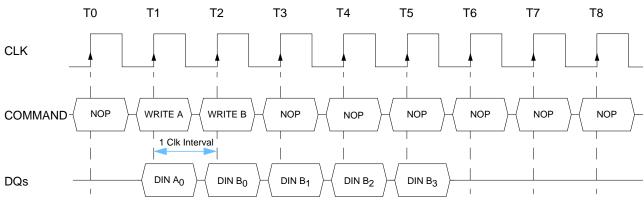

## Write Interrupted by a Write

A burst write operation may be interrupted before completion of the burst. When a burst write cycle is interrupted by a new Write Command, the remaining addresses of the initial write cycle are overridden starting with the new column address applied with the interrupting Write Command. Data will be written into the device until the programmed burst length of the last write command is satisfied.

## Write Interrupted by a Write (Burst Length = 4, CAS Latency = 1, 2, 3)

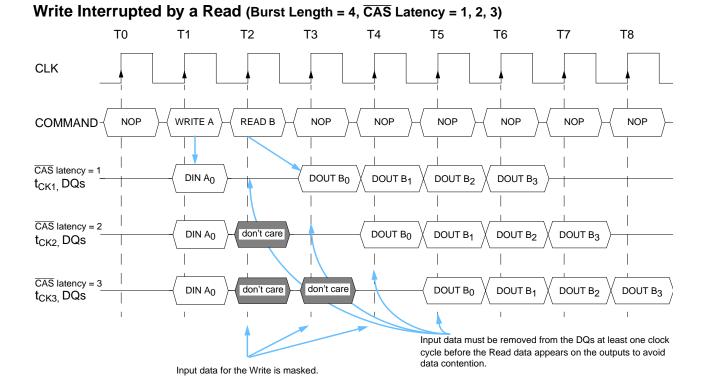

## Write Interrupted by a Read

A Read Command will interrupt a burst write operation on the same clock cycle that the Read Command is registered. The DQs must be in the high impedance state at least one cycle before the interrupting read data appears on the outputs to avoid data contention. When the Read Command is registered, any residual data from the burst write cycle will be ignored. Data that is presented on the DQ pins before the Read Command is initiated will actually be written to the memory.

## **Burst Stop Command**

Once a burst read or write operation has been initiated, there exist several methods in which to terminate the burst operation prematurely. These methods include using another Read or Write Command to interrupt an existing burst operation, using a Precharge Command to interrupt a burst cycle and close the active bank, or using the Burst Stop Command to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank. When interrupting a burst with another Read or Write Command care must be taken to avoid DQ contention. The Burst Stop Command, however, has the fewest restrictions making it the easiest method to use when terminating a burst operation before it has been completed.

The Burst Stop Command is defined by having  $\overline{RAS}$  and  $\overline{CAS}$  high with  $\overline{CS}$  and  $\overline{WE}$  low at the rising edge of the clock. When using the Burst Stop Command during a burst read cycle, the data DQs go to a high impedance state after a delay which is equal to the  $\overline{CAS}$  Latency set in the Mode Register.

## Termination of a Burst Read Operation (Burst Length > 4, TAS Latency = 1, 2, 3)

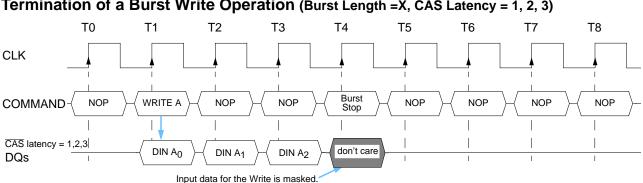

When a Burst Stop Command is issued during a burst write operation, only data presented prior to the Burst Stop command will be written into the device. Any data presented to the device coincident with the Burst Stop command or later will be ignored.

#### Termination of a Burst Write Operation (Burst Length =X, CAS Latency = 1, 2, 3)

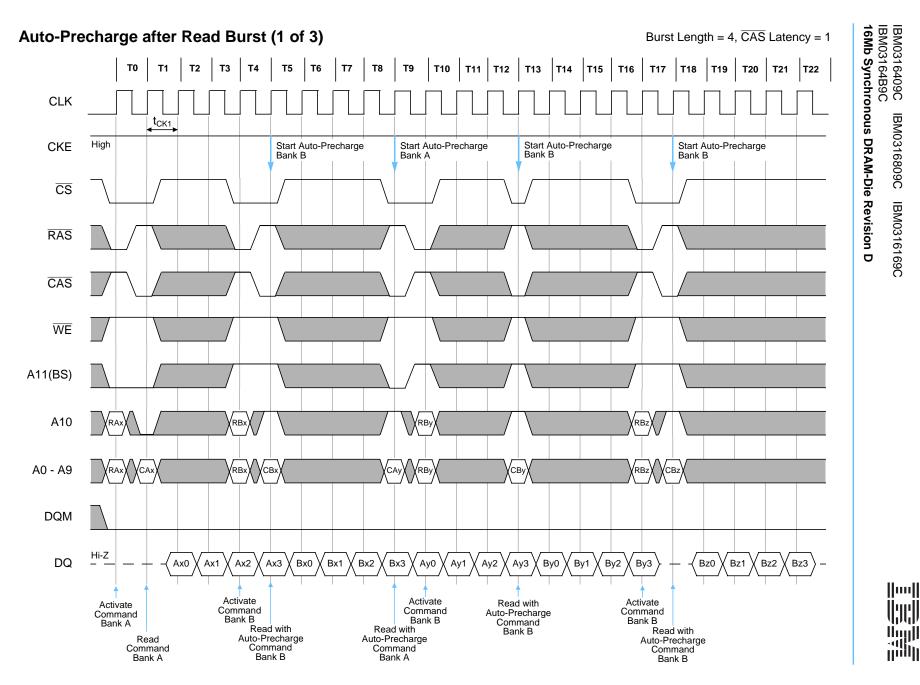

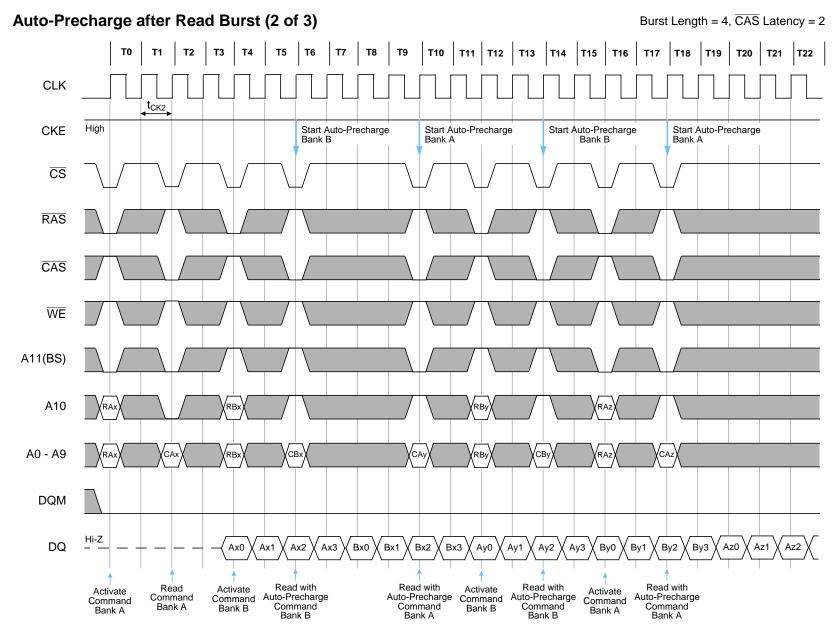

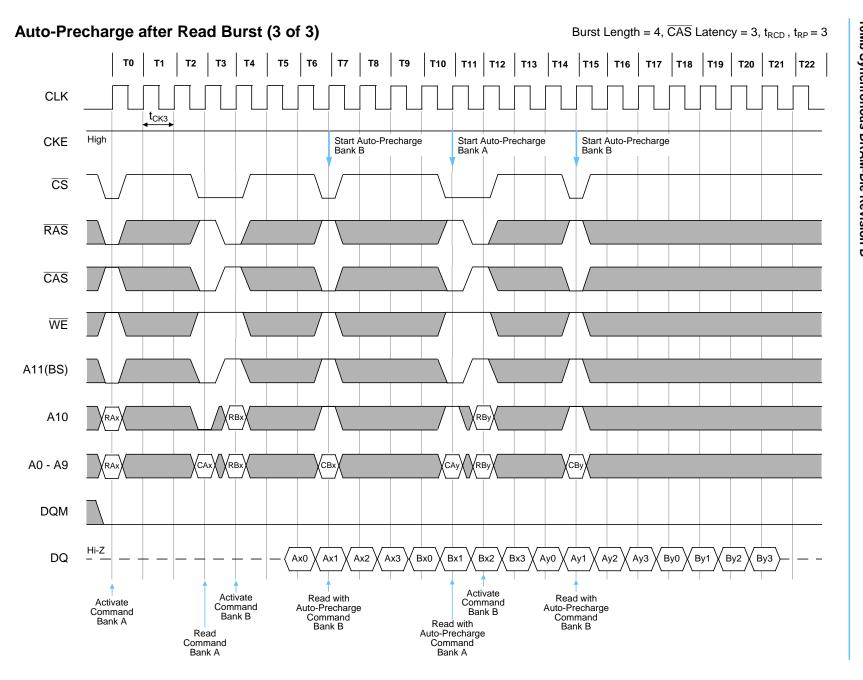

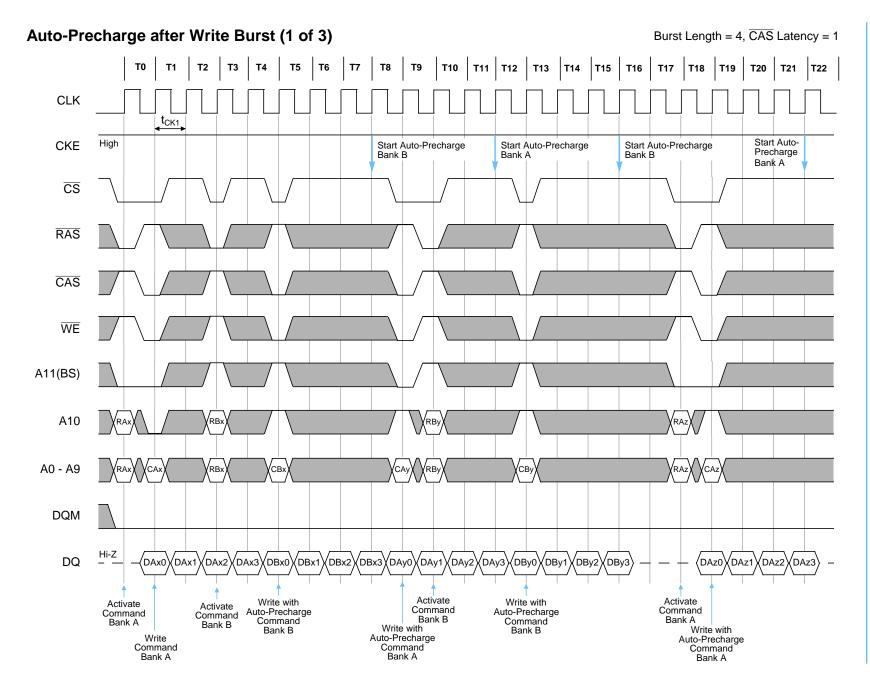

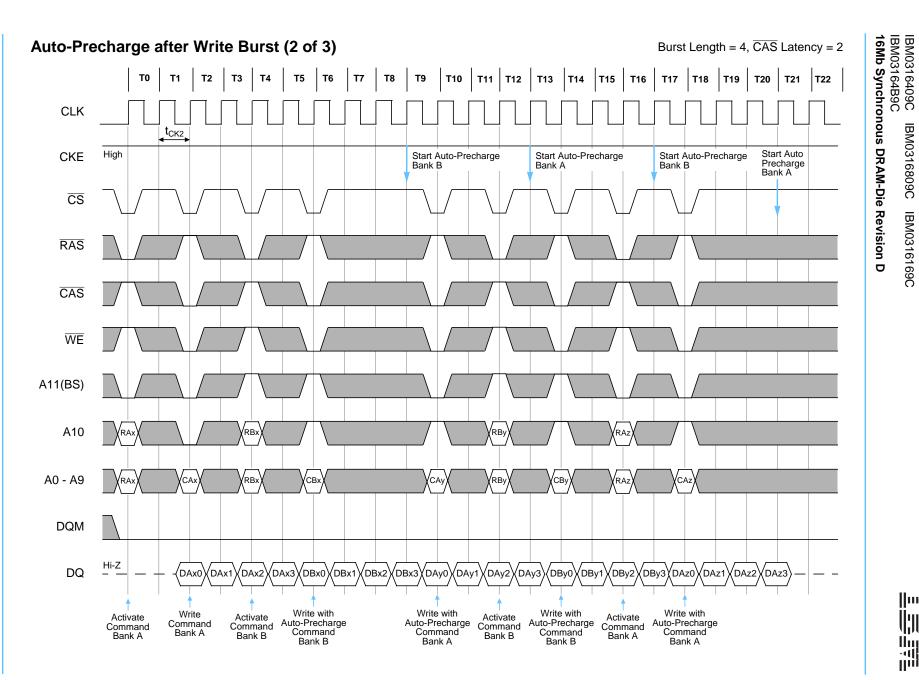

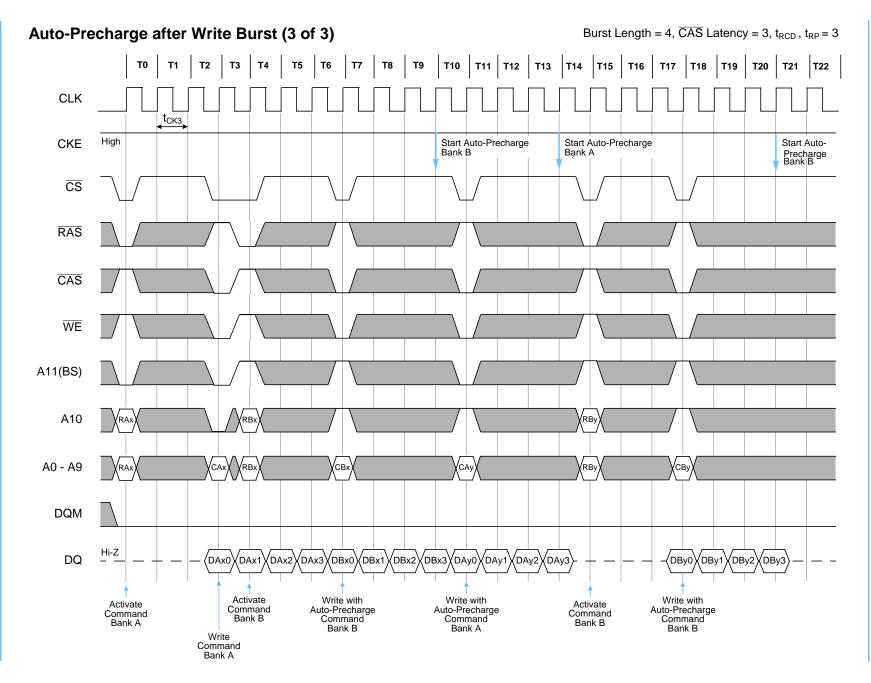

## **Auto-Precharge Operation**

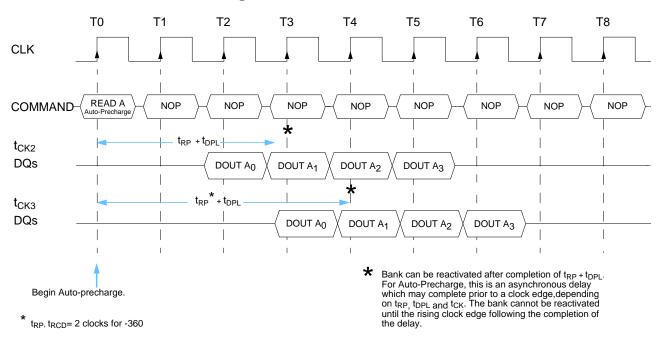

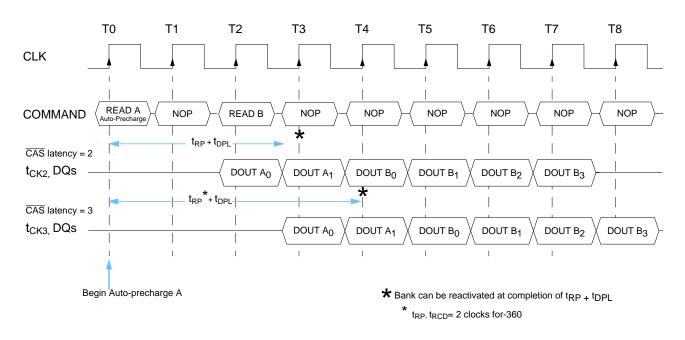

Before a new row in an active bank can be opened, the active bank must be precharged using either the Precharge Command or the auto-precharge function. When a Read or a Write Command is given to the SDRAM, the CAS timing accepts one extra address, column address A10, to allow the active bank to automatically begin precharge at the earliest possible moment during the burst read or write cycle. If A10 is low when the Read or Write Command is issued, then normal Read or Write burst operation is executed and the bank remains active at the completion of the burst sequence. If A10 is high when the Read or Write Command is issued, then the auto-precharge function is engaged. During auto-precharge, a Read Command will execute as normal with the exception that the active bank will begin to precharge immediately and may finish before all burst read cycles have been completed. This feature allows the precharge operation to be partially or completely hidden during the burst read cycles (dependent upon burst length) thus improving system performance for random data access. Auto-precharge can also be implemented during Write commands.

A Read or Write Command without auto-precharge can be terminated in the midst of a burst operation. However, a Read or Write Command with auto-precharge can not be interrupted by a command to the same bank. Therefore use of a Read, Write, Precharge, or Burst Stop Command to the same bank is prohibited during a read or write cycle with auto-precharge until the entire burst operation is completed.

If A10 is high when a Read Command is issued, the Read with auto-precharge function is initiated. Once the precharge operation has started the bank cannot be reactivated until an asynchronous delay time equal to t<sub>RP</sub> + t<sub>DPL</sub> expressed in nanoseconds rather than clocks, has been satisfied. It should be noted that the device will not respond to the Auto-Precharge Command if the device is programmed for full page burst read or write cycles.

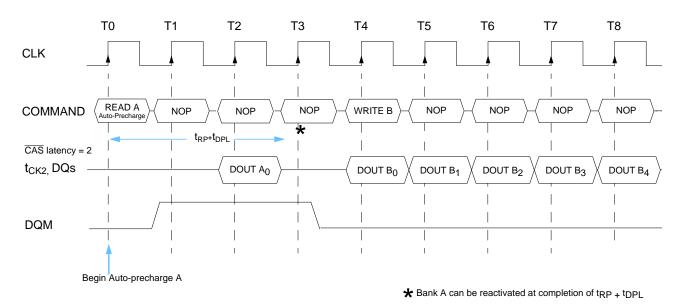

Burst Read with Auto-Precharge (Burst Length = 4)

Although a Read Command with auto-precharge can not be interrupted by a command to the same bank, it can be interrupted by a Read or Write Command to the other bank. The auto-precharge function will begin normally with the issuing command.

If interrupting a Read Command with auto-precharge with a Write Command, DQM must be used to avoid DQ contention.

## Burst Read with Auto-precharge Interrupted by Write (Burst Length = 8, CAS Latency = 2)

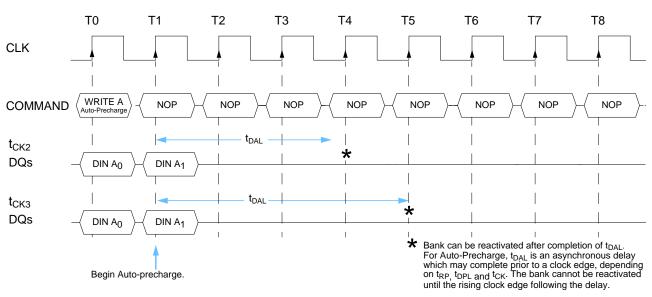

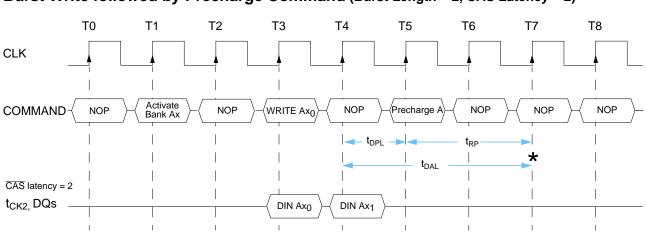

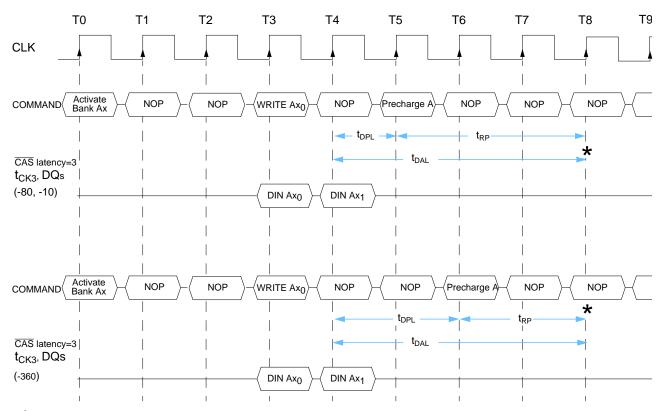

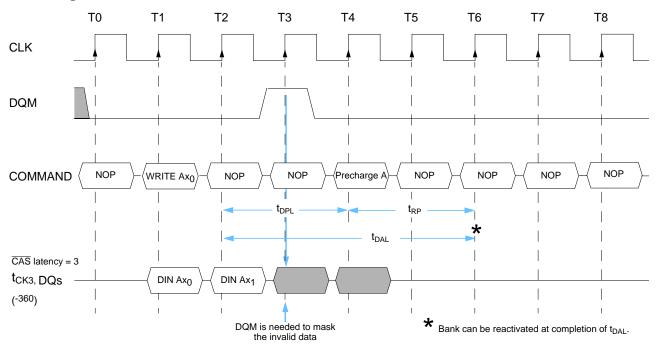

If A10 is high when a Write Command is issued, the Write with auto-precharge function is initiated. The bank undergoing auto-precharge can not be reactivated until  $t_{DPL}$  and  $t_{RP}$  are satisfied. This is referred to as  $t_{DAL}$ , Data-in to Active delay ( $t_{DAL} = t_{DPL} + t_{RP}$ ), and is an asynchronous delay time during auto-precharge.

#### Burst Write with Auto-Precharge (Burst Length = 2)

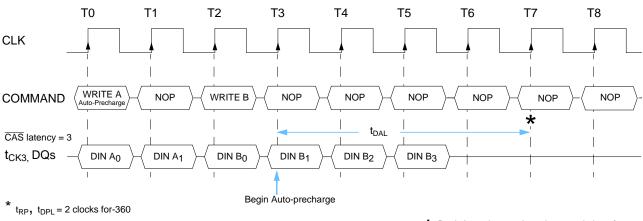

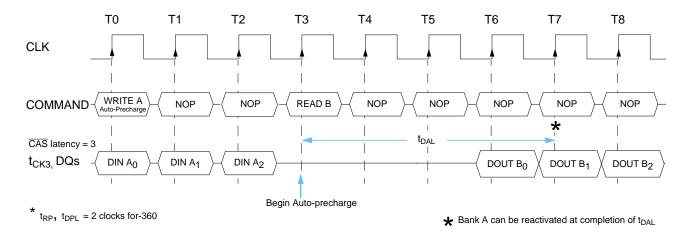

Similar to the Read Command, a Write Command with auto-precharge can not be interrupted by a command to the same bank. It can be interrupted by a Read or Write Command to the other bank, however. The auto-precharge function is unaffected by the interrupting command and will begin as normally scheduled according to burst length.

#### ★ Bank A can be reactivated at completion of t<sub>DAL</sub>

## Burst Write with Auto-Precharge Interrupted by Read (Burst Length = 4, CAS Latency = 3)

## Precharge Command

The Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is triggered when  $\overline{CS}$ ,  $\overline{RAS}$  and  $\overline{WE}$  are low and  $\overline{CAS}$  is high at the rising edge of the clock. The Precharge Command can be used to precharge each bank separately or both banks simultaneously. Two address bits A10 and A11 (BS) are used to define which bank(s) is to be precharged when the command is issued.

#### Bank Selection for Precharge by Address Bits

| A10  | BS(A11)    | Precharged Bank(s) |

|------|------------|--------------------|

| LOW  | LOW        | Bank A only        |

| LOW  | HIGH       | Bank B only        |

| HIGH | DON'T CARE | Both Banks A and B |

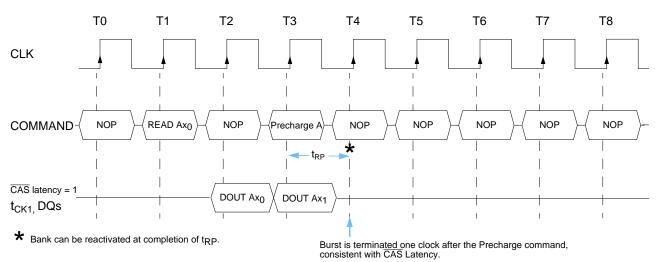

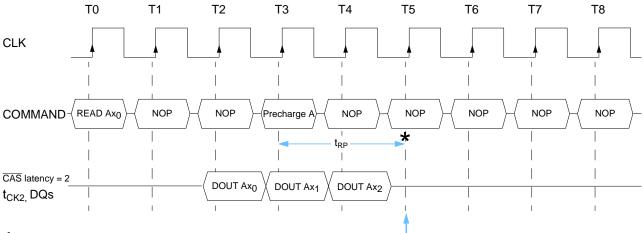

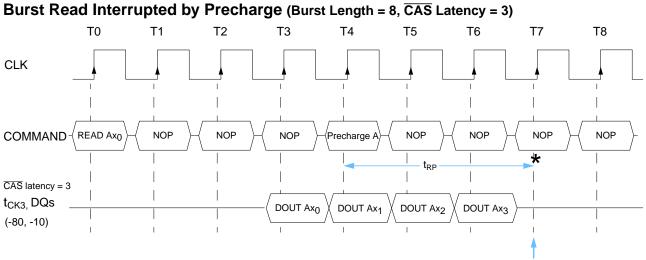

For read cycles, the Precharge Command may be applied consistent with the  $\overline{CAS}$  Latency set in the Mode Register. The data DQs go to a high impedance state after a delay which is equal to the latency, similar to a Burst Stop Command. Refer to the following figures.

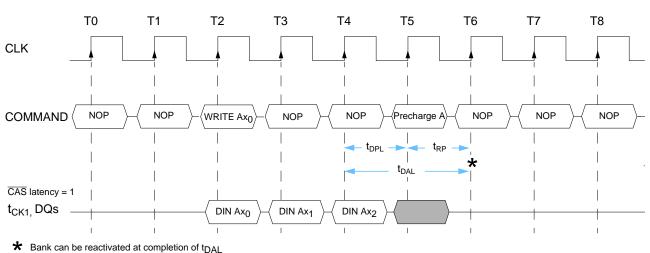

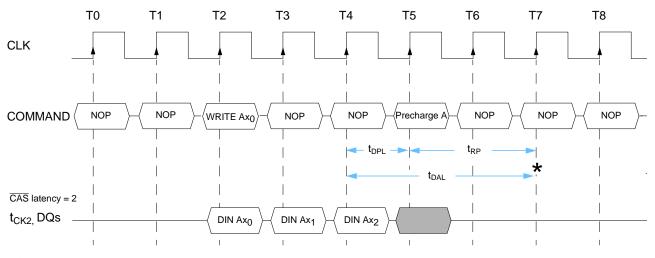

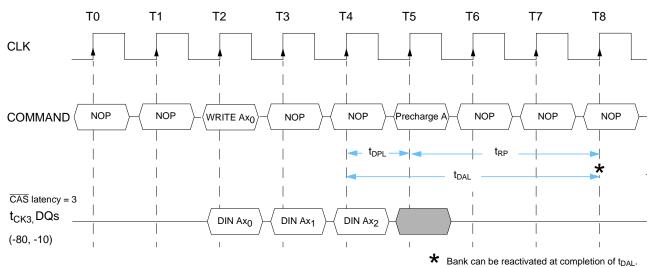

For write cycles, however, a delay must be satisfied from the start of the last burst write cycle until the Precharge Command can be issued. This delay is known as t<sub>DPL</sub>, Data-in to Precharge delay.

After the Precharge Command is issued, the precharged bank must be reactivated before a new read or write access can be executed. The delay between the Precharge Command and the Activate Command must be greater than or equal to the Precharge time ( $t_{RP}$ ).

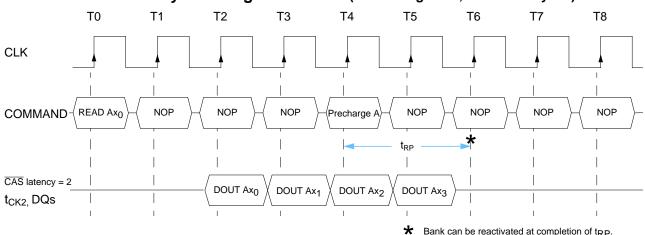

#### Burst Read followed by Precharge Command (Burst Length = 4, CAS Latency = 2)

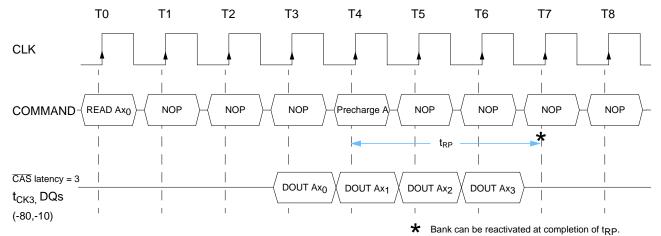

# Burst Read followed by Precharge Command (Burst Length = 4, CAS Latency = 3)

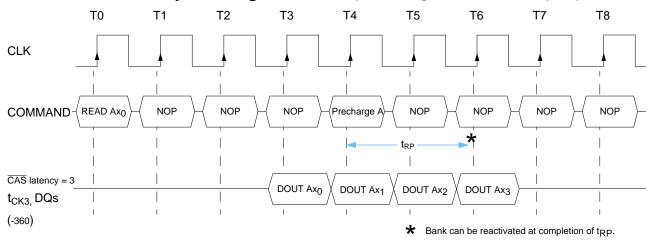

Burst Read followed by Precharge Command (Burst Length = 4, CAS Latency = 3)

## Burst Write followed by Precharge Command (Burst Length = 2, CAS Latency = 2)

\* Bank can be reactivated at completion of  $t_{DAL} (t_{DPL} + t_{RP})$ .

## Burst Write followed by Precharge Command (Burst Length = 2, CAS Latency = 3)

\* Bank can be reactivated at completion of  $t_{DAL} (t_{DPL} + t_{RP})$ .

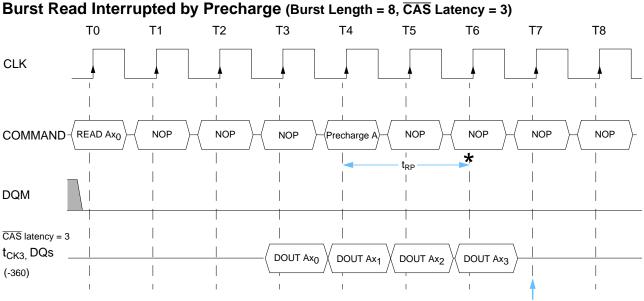

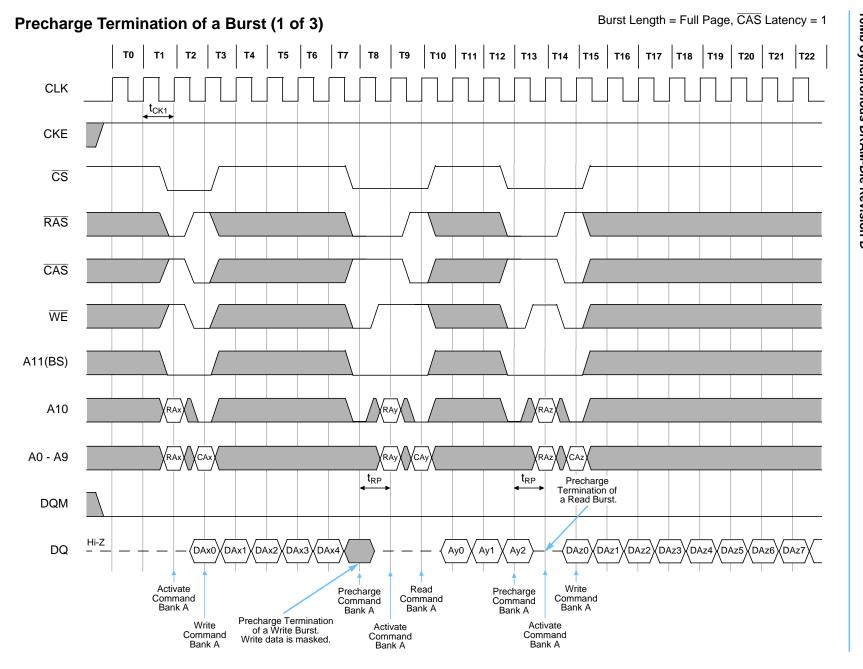

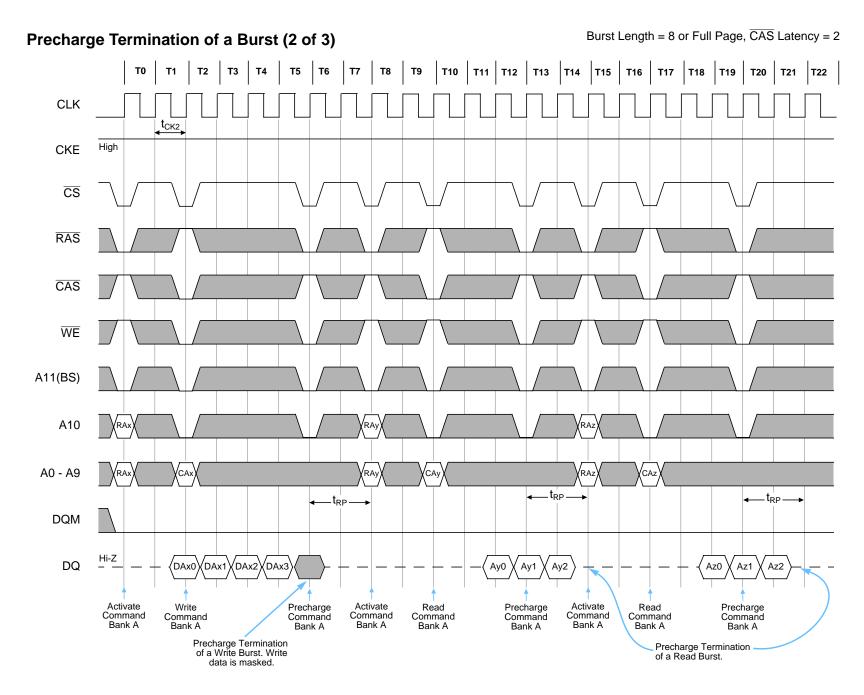

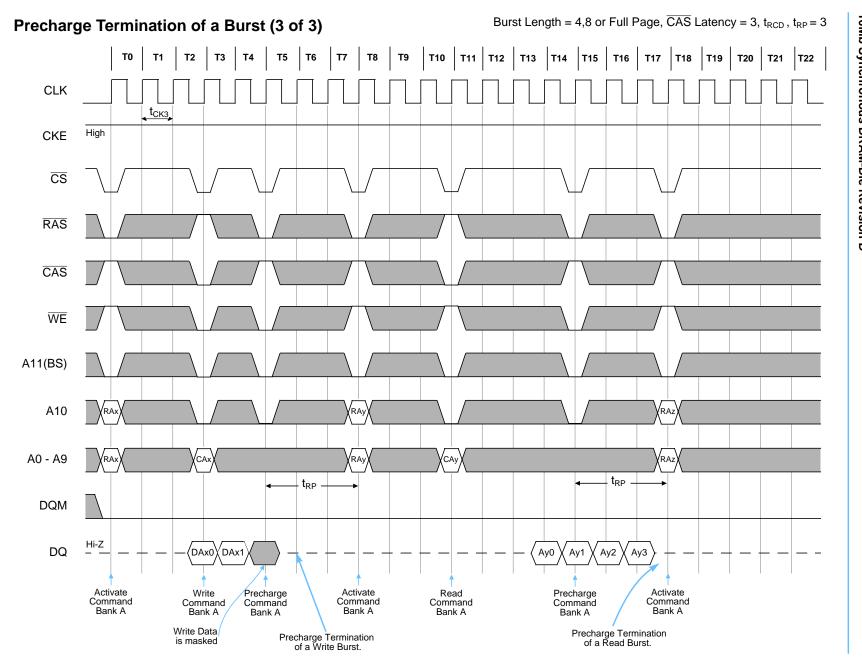

## **Precharge Termination**

The Precharge Command may be used to terminate either a burst read or burst write operation. When the Precharge command is issued, the burst operation is terminated and bank precharge begins. For burst read operations, valid data will continue to appear on the data bus as a function of CAS Latency.

#### Burst Read Interrupted by Precharge (Burst Length = 8, CAS latency = 1)

## Burst Read Interrupted by Precharge (Burst Length = 8, CAS latency = 2)

\* Bank can be reactivated at completion of  $t_{RP}$ .

Burst is terminated two clocks after the Precharge command, consistent with  $\overrightarrow{\text{CAS}}$  Latency.

\* Bank can be reactivated at completion of t<sub>RP</sub>.

Burst is terminated three clocks after the Precharge command, consistent with  $\overrightarrow{\text{CAS}}$  Latency.

\* Bank can be reactivated at completion of t<sub>RP</sub>.

Burst is terminated three clocks after the Precharge command, consistent with  $\overline{\text{CAS}}$  Latency.

Burst write operations will be terminated by the Precharge command. However, write data written to the device prior to the Precharge command may be stored incorrectly and is a function of  $\overline{CAS}$  latency and  $t_{DPL}$ .

When  $\overline{CAS}$  latency is set to equal 1 or 2 or when set to 3 with  $t_{DPL} = 1$  clock, the last write data that will be properly stored in the device is that write data that is presented to the device on the clock cycle prior to the Precharge command. The write data presented during the Precharge command will not be written.

#### **Precharge Termination of a Burst Write (Burst Length = 8, CAS Latency = 1)**

## Precharge Termination of a Burst Write (Burst Length = 8, CAS Latency = 2)

\* Bank can be reactivated at completion of  $t_{DAL}$ .

#### Precharge Termination of a Burst Write (Burst Length = 8, CAS Latency = 3)

When  $\overline{CAS}$  latency is set to equal 3 and  $t_{DPL} = 2$  clocks, the last write data that will be properly stored in the device is that write data that is presented to the device two clocks prior to the Precharge command. The write data presented during the clock cycle prior to the Precharge command may be stored incorrectly. To prevent the writing of invalid data to the device, DQM must be asserted high one clock cycle prior to the Precharge command to mask the invalid write data.

#### Precharge Termination of a Burst Write (Burst Length = 8, CAS Latency = 3)

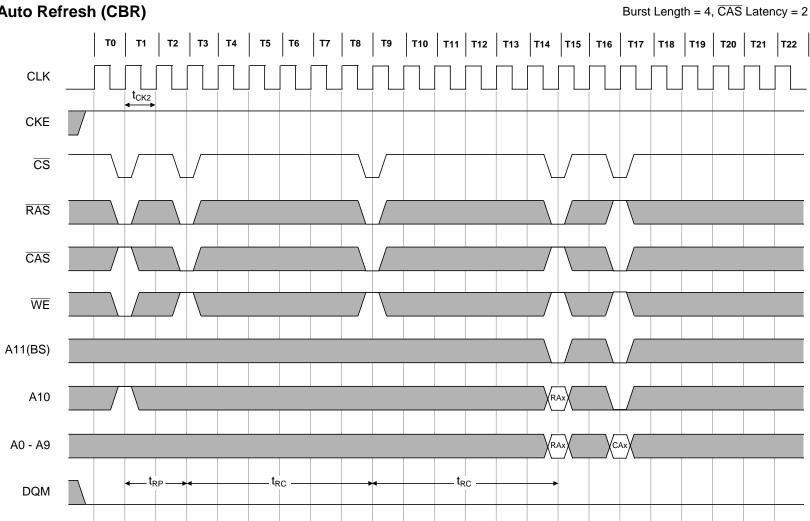

## Automatic Refresh Command (CAS Before RAS Refresh)

When  $\overline{CS}$ ,  $\overline{RAS}$  and  $\overline{CAS}$  are held low with CKE and  $\overline{WE}$  high at the rising edge of the clock, the chip enters the Automatic Refresh mode (CBR). Both banks of the SDRAM must be precharged and idle for a minimum of the Precharge time ( $t_{RP}$ ) before the Auto Refresh Command (CBR) can be applied. For a stacked device, only one deck at a time can be refreshed using Automatic Refresh Mode. An address counter, internal to the device, supplies the bank address during the refresh cycle. No control of the external address pins is required once this cycle has started.

When the refresh cycle has completed, both banks of the SDRAM will be in the precharged (idle) state. A delay between the Auto Refresh Command (CBR) and the next Activate Command or subsequent Auto Refresh Command must be greater than or equal to the RAS cycle time ( $t_{RC}$ ).

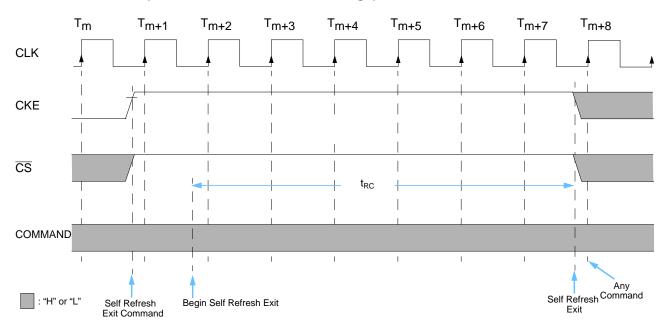

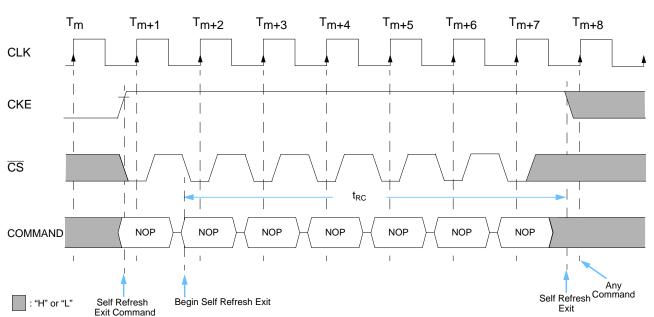

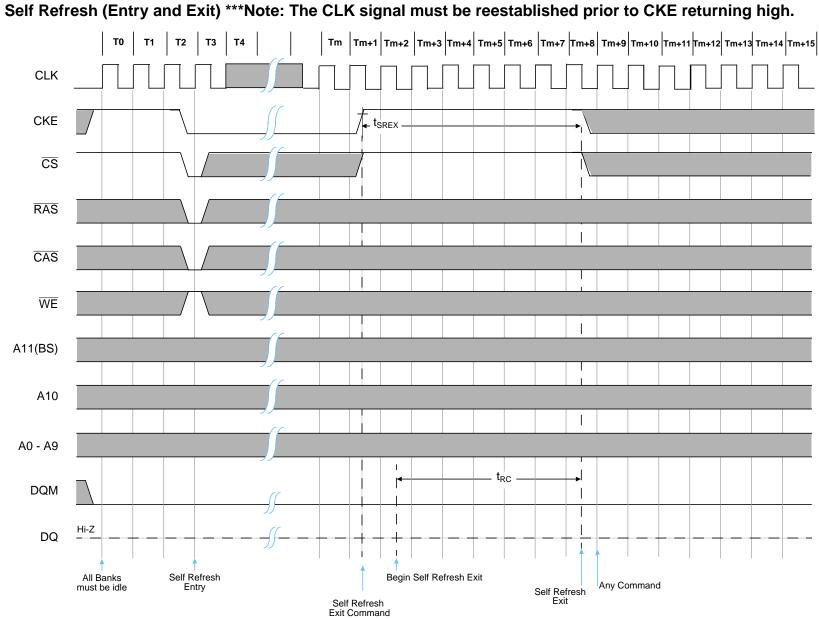

## Self Refresh Command

The SDRAM device has a built-in timer to accommodate Self Refresh operation. The Self Refresh Command is defined by having  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and CKE held low with  $\overline{WE}$  high at the rising edge of the clock. Once the Command is registered, CKE must be held low to keep the device in Self Refresh mode. When the SDRAM has entered Self Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self Refresh Operation to save power. The user may halt the external clock while the device is in Self Refresh mode, however, the clock must be registered asynchronously by bringing CKE high. After CKE is brought high, an internal timer is started to insure CKE is held high for approximately 10ns before registering the Self Refresh exit command. The purpose of this circuit is to filter out noise glitches on the CKE input which may cause the SDRAM to erroneously exit Self Refresh operation. Once the Self Refresh cycle time ( $t_{RC}$ ) must be satisfied before any new command can be issued to the device. CKE must remain high for the entire Self Refresh exit period ( $t_{SREX}$ ) and commands must be gated off with  $\overline{CS}$  held high. Alternatively, NOP commands may be registered on each positive clock edge during the Self Refresh exit interval. (See Self Refresh Exit figures.) When using Self Refresh, both decks of a stacked device may be refreshed at the same time.

#### Self Refresh Exit (Commands Gated Off with CS High)

#### Self Refresh Exit (Commands Gated Off with NOP Commands)

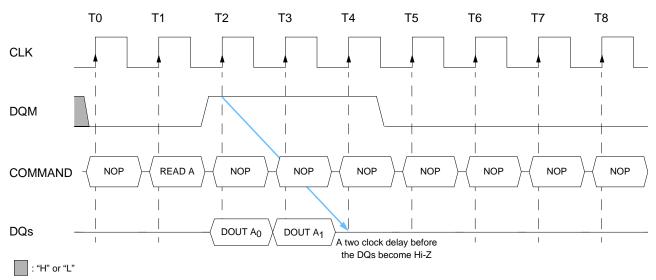

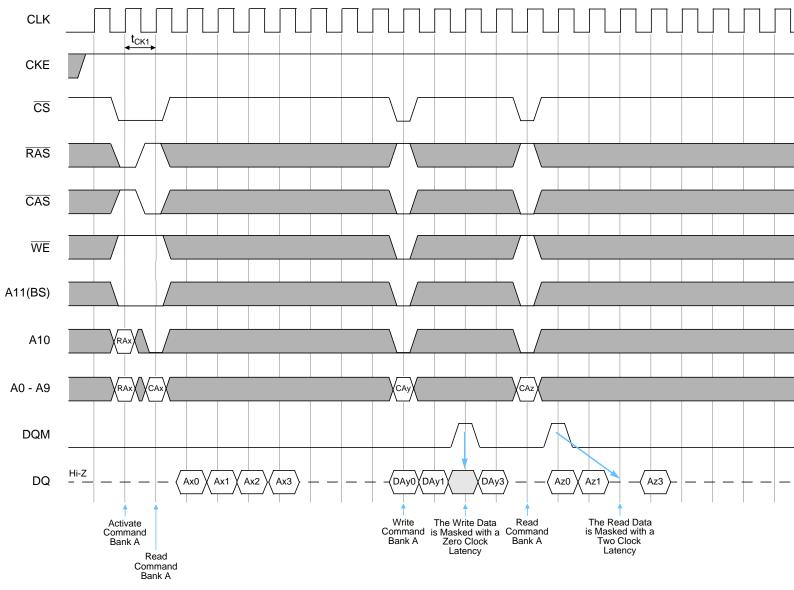

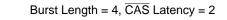

## Data Mask

The SDRAM has a Data Mask function that can be used in conjunction with data read and write cycles. When the Data Mask is high during a write cycle, the write operation is prohibited immediately (zero clock latency). If the Data Mask is activated during a read cycle, the data outputs are disabled and become high impedance after a two clock delay, independent of CAS latency.

## Data Mask Activated During a Read Cycle (Burst Length = 4, CAS Latency = 1)

## No Operation Command

The No Operation Command should be used in cases when the SDRAM is in a idle or a wait state. The purpose of the No Operation Command is to prevent the SDRAM from registering any unwanted commands between operations. A No Operation Command is registered when  $\overline{CS}$  is low with  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle.

## **Deselect Command**

The Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when  $\overline{CS}$  is brought high, the  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  signals become don't cares.

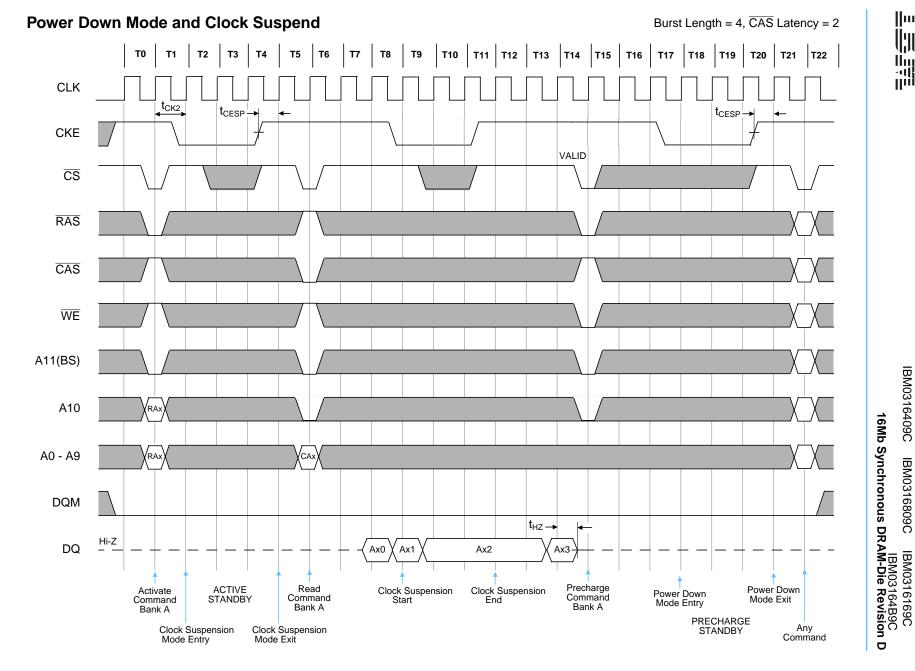

#### Power Down Mode

In order to reduce standby power consumption, two power down modes are available: Precharge and Active Power Down mode. To enter Precharge Power Down mode, all banks must be precharged and the necessary Precharge delay ( $t_{RP}$ ) must occur before the SDRAM can enter the Power Down mode. If a bank is activated but not performing a Read or Write operation, Active Power Down mode will be entered. (Issuing a Power Down Mode Command when the device is performing a Read or Write operation causes the device to enter Clock Suspend mode. See the following section.) Once the Power Down mode is initiated by holding CKE low, all of the receiver circuits except CLK and CKE are gated off. The Power Down mode does not perform any refresh operations, therefore the device can't remain in Power Down mode longer than the Refresh period ( $t_{REF}$ ) of the device.

The Power Down mode is exited by bringing CKE high. A one clock delay after the registration of CKE high is required for the SDRAM to exit the Power Down mode.

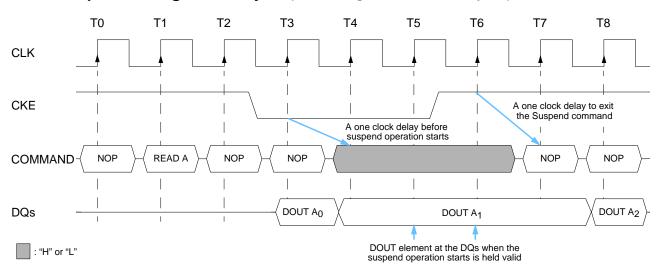

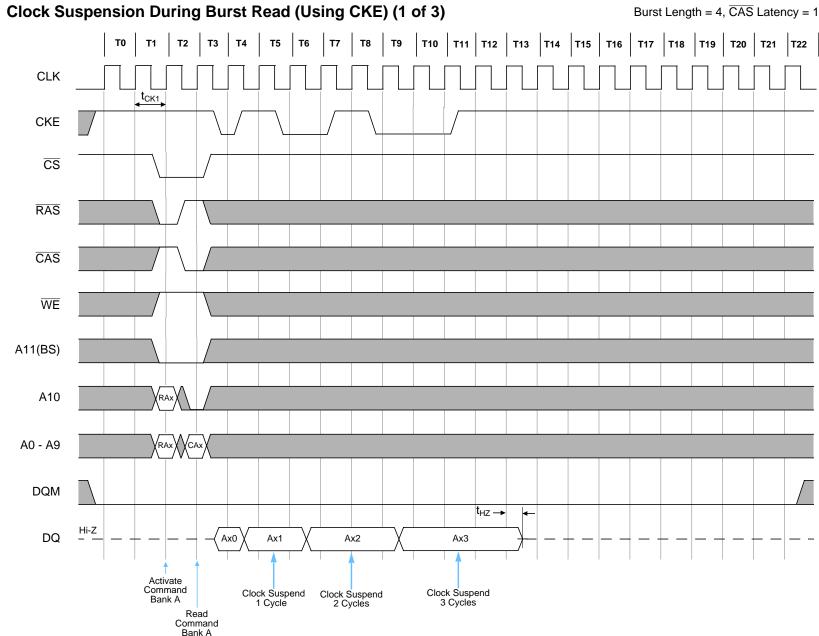

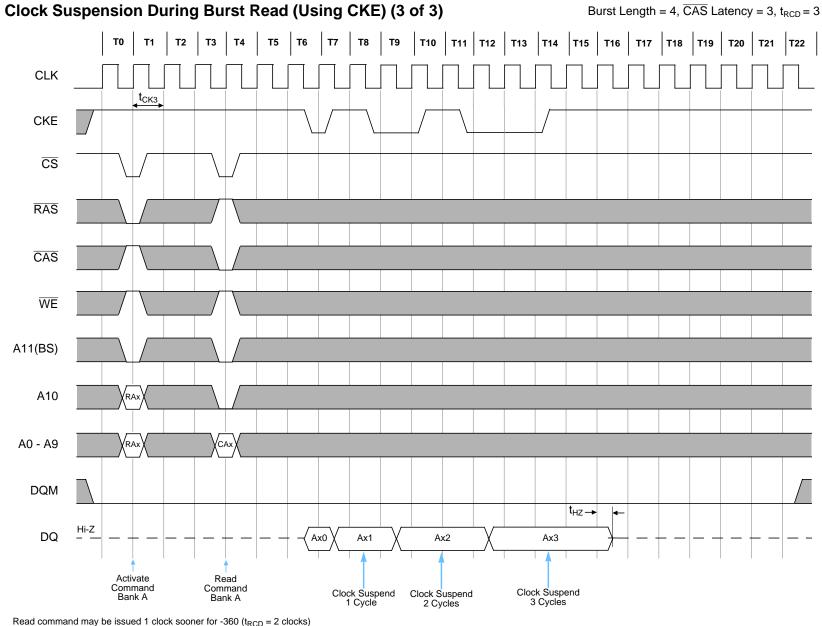

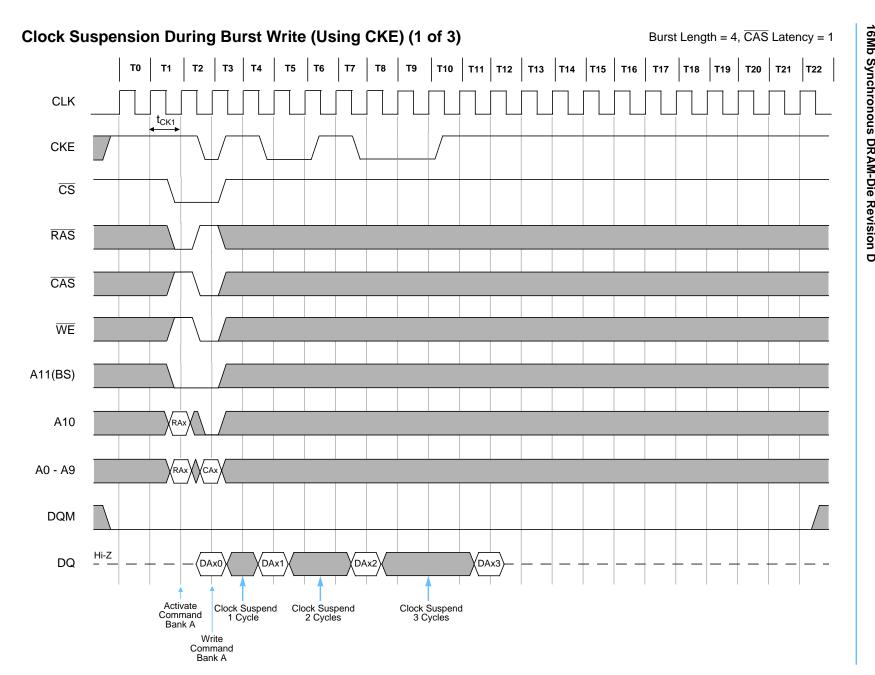

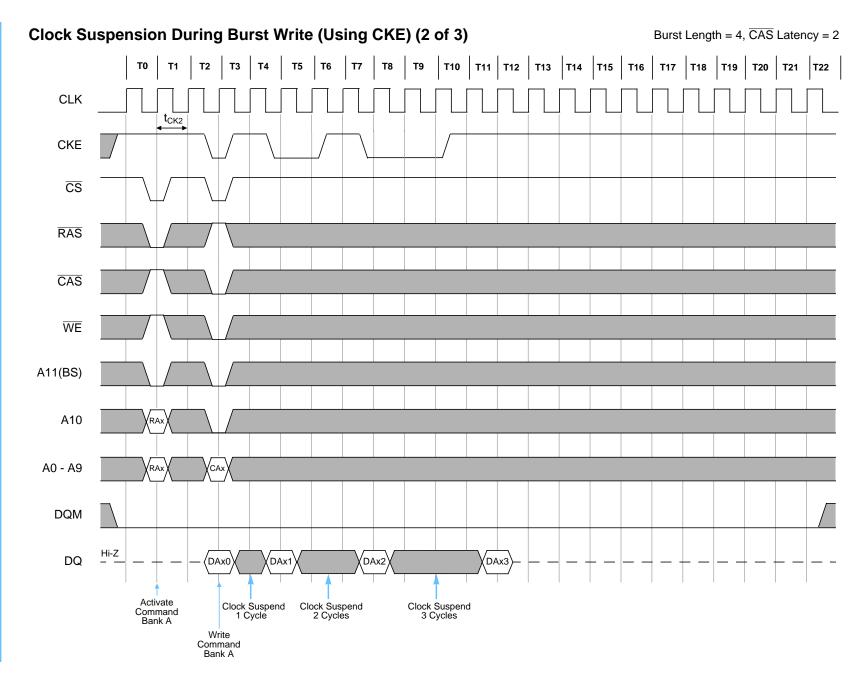

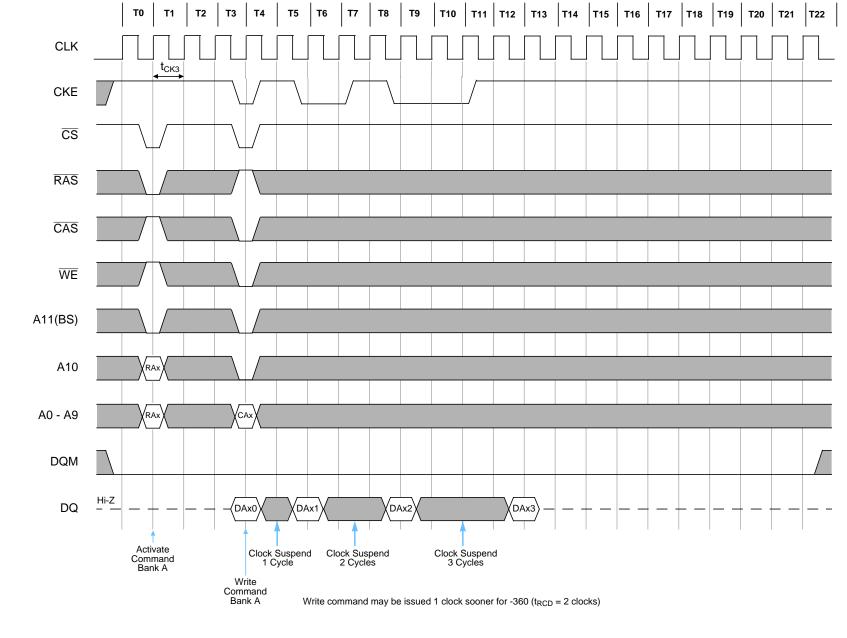

#### Clock Suspend Mode

During normal access mode, CKE is held high enabling the clock. When CKE is registered low while at least one of the banks is active, Clock Suspend Mode is entered. The Clock Suspend mode deactivates the internal clock and suspends or "freezes" any clocked operation that was currently being executed. There is a one clock delay between the registration of CKE low and the time at which the SDRAM's operation suspends. While in Clock Suspend mode, the SDRAM ignores any new commands that are issued. The Clock Suspend mode is exited by bringing CKE high. There is a one clock cycle delay from when CKE returns high to when Clock Suspend mode is exited.

When the operation of the SDRAM is suspended during the execution of a Burst Read operation, the last valid data output onto the DQ pins will be actively held valid until Clock Suspend mode is exited.

#### Clock Suspend During a Read Cycle (Burst Length = 4, CAS latency = 2)

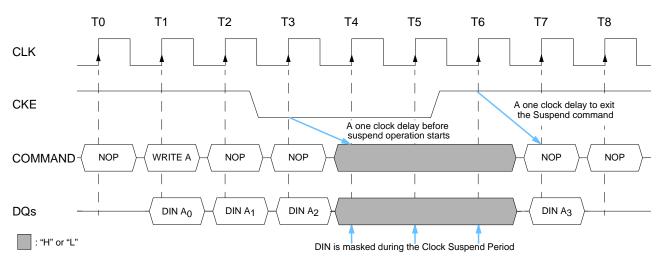

If Clock Suspend mode is initiated during a burst write operation, then the input data is masked and ignored until the Clock Suspend mode is exited.

## Clock Suspend During a Write Cycle (Burst Length = 4, CAS Latency = 2)

## Command Truth Table (Notes: 1)

|                            | Cł                | <Ε               |    |     |     |    |     |     |      |           |       |

|----------------------------|-------------------|------------------|----|-----|-----|----|-----|-----|------|-----------|-------|

| Function                   | Previous<br>Cycle | Current<br>Cycle | CS | RAS | CAS | WE | DQM | A11 | A10  | A9 - A0   | Notes |

| Mode Register Set          | н                 | Х                | L  | L   | L   | L  | Х   |     | OP C | ode       |       |

| Auto (CBR) Refresh         | н                 | н                | L  | L   | L   | н  | х   | х   | х    | х         |       |

| Entry Self Refresh         | н                 | L                | L  | L   | L   | н  | Х   | х   | х    | х         |       |

| Exit Self Refresh          | L                 | н                | н  | х   | х   | х  | Х   | х   | х    | х         |       |

| Single Bank Precharge      | н                 | х                | L  | L   | н   | L  | х   | BS  | L    | х         | 2     |

| Precharge all Banks        | н                 | Х                | L  | L   | н   | L  | х   | х   | н    | х         |       |

| Bank Activate              | н                 | х                | L  | L   | н   | н  | х   | BS  | Rov  | v Address | 2     |

| Write                      | н                 | х                | L  | н   | L   | L  | х   | BS  | L    | Column    | 2     |

| Write with Auto-Precharge  | н                 | Х                | L  | н   | L   | L  | х   | BS  | н    | Column    | 2     |

| Read                       | н                 | х                | L  | н   | L   | н  | х   | BS  | L    | Column    | 2     |

| Read with Auto-Precharge   | н                 | х                | L  | н   | L   | н  | х   | BS  | н    | Column    | 2     |

| Burst Termination          | н                 | Х                | L  | н   | н   | L  | х   | х   | х    | х         | 3     |

| No Operation               | н                 | х                | L  | н   | н   | н  | х   | х   | х    | х         |       |

| Device Deselect            | н                 | Х                | н  | х   | х   | х  | х   | Х   | х    | х         |       |

| Clock Suspend/Standby Mode | L                 | Х                | х  | х   | х   | х  | х   | Х   | х    | х         | 4     |

| Data Write/Output Enable   | н                 | Х                | х  | х   | х   | х  | L   | Х   | х    | х         | 5     |

| Data Mask/Output Disable   | н                 | Х                | х  | х   | х   | х  | н   | х   | х    | х         | 5     |

| Power Down Mode Entry      | Х                 | L                | х  | х   | х   | х  | х   | Х   | х    | х         | 6, 7  |

| Power Down Mode Exit       | х                 | н                | Х  | Х   | х   | х  | х   | Х   | Х    | х         | 6, 7  |

1. All of the SDRAM operations are defined by states of CS, WE, RAS, CAS, and DQM at the positive rising edge of the clock. For stacked devices: only one deck can be operated at once, except during Self Refresh.

2. Bank Select (BS), if BS = 0 then bank A is selected, if BS = 1 then bank B is selected.

3. During a Burst Write cycle there is a zero clock delay, for a Burst Read cycle the delay is equal to the CAS latency.

4. During normal access mode, CKE is held high and CLK is enabled. When it is low, it freezes the internal clock and extends data Read and Write operations. One clock delay is required for mode entry and exit.

5. The DQM has two functions for the data DQ Read and Write operations. During a Read cycle, when DQM goes high at a clock timing the data outputs are disabled and become high impedance after a two clock delay. DQM also provides a data mask function for Write cycles. When it activates, the Write operation at the clock is prohibited (zero clock latency).

6. All banks must be precharged before entering the Precharge Power Down Mode. If banks are active, Active Power Down Mode is entered. The Power Down Mode does not perform any refresh operations, therefore the device can't remain in this mode longer than the Refresh period (t<sub>REF</sub>) of the device. One clock delay is required for mode entry and exit.

7. If CS is low, then when CKE returns high, no command is registered into the chip for one clock cycle.

## Clock Enable (CKE) Truth Table

|                         | Cł                | <Ε               |    |     | Con | nmand |     |          |                                                                     |       |

|-------------------------|-------------------|------------------|----|-----|-----|-------|-----|----------|---------------------------------------------------------------------|-------|

| Current State           | Previous<br>Cycle | Current<br>Cycle | CS | RAS | CAS | WE    | A11 | A10 - A0 | Action                                                              | Notes |

|                         | Н                 | Х                | Х  | Х   | Х   | Х     | Х   | Х        | INVALID                                                             | 1     |

|                         | L                 | н                | н  | Х   | Х   | Х     | Х   | Х        | Exit Self Refresh with Device Deselect                              | 2     |

|                         | L                 | н                | L  | н   | н   | н     | Х   | Х        | Exit Self Refresh with No Operation                                 | 2     |

| Self Refresh            | L                 | н                | L  | н   | н   | L     | Х   | х        | ILLEGAL                                                             | 2     |

|                         | L                 | н                | L  | н   | L   | Х     | Х   | х        | ILLEGAL                                                             | 2     |

|                         | L                 | н                | L  | L   | Х   | Х     | Х   | х        | ILLEGAL                                                             | 2     |

|                         | L                 | L                | Х  | Х   | Х   | Х     | Х   | х        | Maintain Self Refresh                                               |       |

|                         | н                 | х                | Х  | Х   | Х   | Х     | Х   | х        | INVALID                                                             | 1     |

| Davias Davis            | L                 | н                | н  | Х   | Х   | Х     | Х   | х        | Power Down mode exit, all banks idle                                | 2     |

| Power Down              | L                 | н                | L  | Х   | Х   | Х     | Х   | х        | ILLEGAL                                                             | 2     |

|                         | L                 | L                | Х  | Х   | Х   | Х     | Х   | х        | Maintain Power Down Mode                                            |       |

|                         | н                 | н                | н  | Х   | Х   | Х     |     |          |                                                                     | 3     |

|                         | н                 | н                | L  | н   | Х   | Х     |     |          | Refer to the Idle State section of the<br>Current State Truth Table | 3     |

|                         | н                 | н                | L  | L   | н   | Х     |     |          |                                                                     | 3     |

|                         | н                 | н                | L  | L   | L   | н     | Х   | Х        | CBR Refresh                                                         |       |

|                         | н                 | н                | L  | L   | L   | L     | OF  | Code     | Mode Register Set                                                   | 4     |

| All Banks Idle          | н                 | L                | н  | Х   | Х   | Х     |     |          |                                                                     | 3     |

|                         | н                 | L                | L  | н   | Х   | Х     |     |          | Refer to the Idle State section of the<br>Current State Truth Table | 3     |

|                         | н                 | L                | L  | L   | н   | Х     |     |          |                                                                     | 3     |

|                         | н                 | L                | L  | L   | L   | н     | Х   | Х        | Entry Self Refresh                                                  | 4     |

|                         | н                 | L                | L  | L   | L   | L     | OF  | o Code   | Mode Register Set                                                   |       |

|                         | L                 | х                | х  | х   | х   | Х     | Х   | Х        | Power Down                                                          | 4     |

|                         | Н                 | Н                | х  | х   | х   | х     | х   | х        | Refer to operations in the Current<br>State Truth Table             |       |

| Any State<br>other than | н                 | L                | Х  | Х   | Х   | Х     | х   | Х        | Begin Clock Suspend next cycle                                      | 5     |

| listed above            | L                 | н                | Х  | Х   | Х   | Х     | Х   | х        | Exit Clock Suspend next cycle                                       |       |

|                         | L                 | L                | Х  | Х   | Х   | Х     | Х   | Х        | Maintain Clock Suspend                                              |       |

1. For the given Current State, CKE must be low in the previous cycle.

2. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. The minimum setup time for CKE (t<sub>CES</sub>) must be satisfied before any command other than Exit is issued.

3. The address inputs (A11 - A0) depend on the command that is issued. See the Idle State section of the Current State Truth Table for more information.

4. The Power Down Mode, Self Refresh Mode, and the Mode Register Set can only be entered from the all banks idle state.

5. Must be a legal command as defined in the Current State Truth Table.

## Current State Truth Table (Part 1 of 4) (Notes: 1)

| Current State |                        |     |     |    | С   | ommand      |                      | Start Auto or Self Refresh<br>No Operation<br>Activate the specified bank and row<br>ILLEGAL<br>ILLEGAL<br>No Operation<br>No Operation<br>No Operation or Power Down<br>ILLEGAL<br>ILLEGAL<br>Precharge<br>ILLEGAL<br>Start Write; Determine if Auto-Precharg<br>Start Read; Determine if Auto-Precharg<br>No Operation<br>No Operation<br>No Operation<br>No Operation<br>ILLEGAL<br>ILLEGAL<br>ILLEGAL<br>ILLEGAL | Notes |

|---------------|------------------------|-----|-----|----|-----|-------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Current State | $\overline{\text{CS}}$ | RAS | CAS | WE | A11 | A10 - A0    | Description          | Action                                                                                                                                                                                                                                                                                                                                                                                                               | notes |

|               | L                      | L   | L   | L  |     | OP Code     | Mode Register Set    | Set the Mode Register                                                                                                                                                                                                                                                                                                                                                                                                | 2     |

|               | L                      | L   | L   | н  | Х   | Х           | Auto or Self Refresh | Start Auto or Self Refresh                                                                                                                                                                                                                                                                                                                                                                                           | 2, 3  |

|               | L                      | L   | н   | L  | BS  | Х           | Precharge            | No Operation                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|               | L                      | L   | н   | Н  | BS  | Row Address | Bank Activate        | Activate the specified bank and row                                                                                                                                                                                                                                                                                                                                                                                  |       |

| Idle          | L                      | н   | L   | L  | BS  | Column      | Write w/o Precharge  | ILLEGAL                                                                                                                                                                                                                                                                                                                                                                                                              | 4     |

|               | L                      | н   | L   | н  | BS  | Column      | Read w/o Precharge   | ILLEGAL                                                                                                                                                                                                                                                                                                                                                                                                              | 4     |

|               | L                      | н   | н   | L  | Х   | Х           | Burst Termination    | No Operation                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|               | L                      | н   | н   | н  | Х   | Х           | No Operation         | No Operation                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|               | н                      | Х   | Х   | Х  | Х   | Х           | Device Deselect      | No Operation or Power Down                                                                                                                                                                                                                                                                                                                                                                                           | 5     |

|               | L                      | L   | L   | L  |     | OP Code     | Mode Register Set    | ILLEGAL                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|               | L                      | L   | L   | н  | Х   | Х           | Auto or Self Refresh | ILLEGAL                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|               | L                      | L   | н   | L  | BS  | Х           | Precharge            | Precharge                                                                                                                                                                                                                                                                                                                                                                                                            | 6     |

|               | L                      | L   | н   | н  | BS  | Row Address | Bank Activate        | ILLEGAL                                                                                                                                                                                                                                                                                                                                                                                                              | 4     |

| Row Active    | L                      | н   | L   | L  | BS  | Column      | Write                | Start Write; Determine if Auto-Precharge                                                                                                                                                                                                                                                                                                                                                                             | 7, 8  |

|               | L                      | н   | L   | н  | BS  | Column      | Read                 | Start Read; Determine if Auto-Precharge                                                                                                                                                                                                                                                                                                                                                                              | 7, 8  |